# Introduction au langage VHDL Synthétisable

Jean Louis BOIZARD Maître de conférences IUFM Midi-Pyrénées

> Master 1 ISME Version 1.5

# SOMMAIRE

| 1) | Generantes                             |                                  |                                                                            |                                                                                                                     |                                        |  |

|----|----------------------------------------|----------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

|    | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Histor<br>Termi<br>VHDI<br>Synth | uction<br>rique<br>nologie<br>L et les autre<br>èse du VHD<br>s de dévelop | L                                                                                                                   | p 3<br>p 3<br>p 3<br>p 3<br>p 3<br>p 4 |  |

| 2) | Bases de VHDL                          |                                  |                                                                            |                                                                                                                     |                                        |  |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5        | Les lil<br>L'enti<br>L'arcl      | uction<br>brairies<br>té<br>nitecture<br>lisation des a                    | architectures                                                                                                       | p 4<br>p 5<br>p 5<br>p 6               |  |

|    |                                        | 2.5.2<br>2.5.3                   |                                                                            | eurs<br>tions conditionnelles<br>tions sélectives                                                                   | p 8<br>p 9<br>p 9<br>p 9<br>p 9        |  |

|    |                                        |                                  | 2.5.5.1<br>2.5.5.2<br>2.5.5.3<br>2.5.5.4                                   | Les variables Syntaxe d'un process Affectation des signaux Instructions séquentielles                               | p 9<br>p 9<br>p 10<br>p 10             |  |

|    |                                        | 2.5.6 Exemples                   |                                                                            |                                                                                                                     |                                        |  |

|    |                                        |                                  | 2.5.6.1<br>2.5.6.2<br>2.5.6.3<br>2.5.6.4<br>2.5.6.5                        | Instruction IF THEN ELSE<br>Instruction FORLOOP<br>Paramètres génériques<br>Instruction CASE<br>Additionneur 4 bits | p10<br>p11<br>p13<br>p13<br>p14        |  |

| 3) | La cor                                 | nception                         | n haut niveau                                                              | 1                                                                                                                   |                                        |  |

|    | 3.1<br>3.2<br>3.3                      | 3.2 Codage des machines à états  |                                                                            |                                                                                                                     | p 16<br>p 18<br>p 21                   |  |

## 1) GENERALITES

## 1.1) INTRODUCTION

Le langage VHDL signifie:

VHSIC (Very High Speed Integrated Circuit)

Hardware

**D**escription

Language

C'est un standard de L'IEEE (Institute of Electrical and Electronics Engineers). C'est un langage de description de haut niveau pour la simulation et la synthèse de circuits électroniques numériques.

## 1.2) HISTORIQUE

- 1980: projet du DoD ( Department of Defense) américain de créer un langage standard de description des circuits intégrés à haute vitesse ( programme VHSIC).

- 1987: IEEE adopte VHDL comme une norme (norme IEEE 1076).

- 1993: Révision et enrichissement de la norme (la norme devient IEEE 1076-93 puis IEEE-1164)

## 1.3) TERMINOLOGIE

- HDL: le langage de description matérielle est un logiciel de programmation permettant la description d'un ensemble ou sous-ensemble matériel.

- description comportementale: le circuit est décrit fonctionnellement et ne fait pas appel à des structures électroniques.

(Cette description est utilisable aussi bien pour la simulation que pour la synthèse).

- description structurelle: le circuit est décrit par des interconnexions de composants ou primitives de plus bas niveau.

- 1.4) VHDL et les autres standards

- VHDL: " Dites-moi comment vous voulez que votre application se comporte et je vous fournirai les circuits correspondants".

- ABEL, PALASM, AHDL: " Dites-moi quels circuits vous voulez et je vous les fournirai".

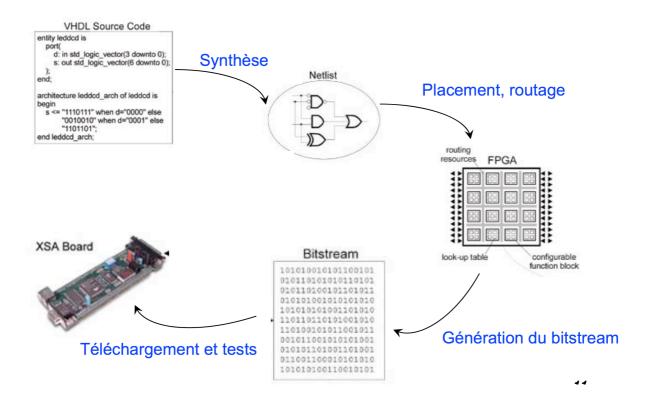

#### 1.5) SYNTHESE DU VHDL

Il ne faut pas oublier que pour l'électronicien la finalité d'une description en langage VHDL est la réalisation d'un ou plusieurs circuits électroniques réalisant les fonctions souhaitées. On distingue alors deux aspects:

- le VHDL synthétisable pour lequel le compilateur sait générer la circuiterie adéquate.

- le VHDL non synthétisable pour lequel le compilateur ne sait pas traduire en circuits les fonctions demandées.

On peut s'interroger quant à l'intérêt d'une description VHDL qui ne serait pas synthétisable. La raison tient en fait à la puissance et au succès de ce langage. Très vite avec l'évolution des besoins et la complexité des circuits électroniques, une méthode rigoureuse et puissante de description des circuits est devenue indispensable. On peut faire le parallèle à ce sujet avec l'évolution du génie logiciel et les apparitions des méthodes de spécification (SADT, SART, OMT, UML...). Un des avantages fondamentaux de VHDL est qu'il peut traduire un cahier des charges complexe et en assurer la simulation: il devient donc un outil de spécification et de simulation. C'est du ressort de l'électronicien de voir comment une description non synthétisable a priori par le compilateur peut être malgré tout traduite en circuits. C'est également une des raisons pour lesquelles le langage VHDL est avant tout un **outil d'électronicien.**

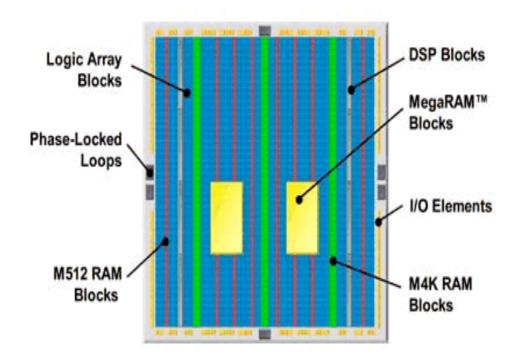

Nota: Les plateformes de développement de FPGA (LATTICE, ALTERA, XILINX, ACTEL...) n'acceptent que du langage VHDL synthétisable.

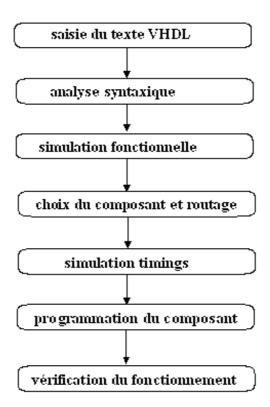

## 1.6) ETAPES DE DEVELOPPEMENT

## 2) BASES DE VHDL

## 2.1) INTRODUCTION

- Tout comme la saisie de schéma, le langage VHDL fait appel à des LIBRAIRIES.

- Il peut effectuer de la simulation et de la synthèse.

- Il utilise des mots clés:

- \* les lignes de commande sont terminées par "; ".

- \* les "blancs" n'ont pas d'effet (utilisés pour la lisibilité).

- \* les commentaires sont précédés de " -- ".

- \* On peut utiliser indifféremment les majuscules ou les minuscules cependant les mots clés sont souvent mis en majuscules.

- les modèles peuvent être décrits en

- \* comportemental

- \* structurel

- \* mixte (les deux précédents).

- Il utilise les concepts de base suivants:

- \* L'ENTITE (ENTITY)

\* L'ARCHITECTURE (ARCHITECTURE)

\* LA CONFIGURATION (CONFIGURATION)

\* Le BOÎTIER (PACKAGE)

## 2.2) LES LIBRAIRIES

Celles-ci sont déclarées en début du fichier VHDL. Les plus usuelles sont:

- IEEE.std logic 1164.all;

- IEEE.std logic arith.all;

- IEEE.std logic signed.all;

- IEEE.std logic unsigned.all;

Ainsi pour une application faisant appel à de la logique combinatoire et séquentielle (le plus fréquent) on trouvera en début de fichier:

# Library IEEE; use IEEE.std logic 1164.all;

Cette librairie (issue de la révision de 1993) permet de travailler sur des signaux, variables, entrées-sorties de type BIT, BOOLEEN, ENTIER, REEL et supporte tous les opérateurs associés.

Afin d'optimiser les temps de développement et le "time to market" les constructeurs de circuits programmables proposent des librairies de macro fonctions.

## exemple:

La librairie **LPM** (Library of Parametrized Modules) de chez ALTERA propose un ensemble de macro fonctions ( additionneurs n bits, multiplieurs...) optimisées pour ses circuits. Pour l'appeler:

# library lpm;

## use lpm.lpm components.all;

Par ailleurs les constructeurs proposent sur leurs sites Web un bon nombre de macro fonctions mises en libre service (filtres numériques, arbitre de bus VME, codeurs, cœurs de CPU...).

#### 2.3) L'ENTITE

Elle donne une vue extérieure du modèle VHDL réalisé. Elle s'apparente à un symbole. Syntaxe:

**ENTITY** <nom entité> IS

Déclarations génériques;

Déclaration des ports;

**END** <nom entité>;

où **<nom\_entité>** est le nom donné au modèle VHDL (ex: multiplexeur, additionneur...).

<u>Remarque:</u> dans ALTERA le fichier VHDL doit porter le même nom que l'entité. En conséquence si l'entité s'appelle **multiplexeur** le fichier s'intitulera: **multiplexeur.vhd**

## - Déclarations génériques:

Utilisées pour passer des informations au modèle. C'est le cas lorsqu'on veut avoir un modèle générique réutilisable (exemple: générateur de parité de taille N. La valeur de N est passée en paramètre générique).

Exemple:

#### LIBRARY ieee;

USE ieee.std\_logic\_1164.all;

## **ENTITY** parite taille IS

generic (taille : integer :=16);

PORT (op1 : IN bit vector (taille-1 downto 0);

parite : OUT bit);

END parite taille;

## - Déclaration des ports:

Elle permet de décrire les broches d'entrées et de sorties du modèle.

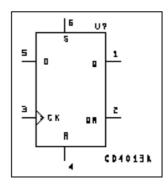

# exemple 1: bascule D CD4013A avec Set et Reset

## Library IEEE;

**USE IEEE.std logic 1164.all**;

**ENTITY CD4013A IS**

port (CK, D, S, R : in std\_logic; Q, QN : out std\_logic );

**END CD4013A**;

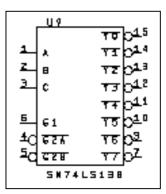

# exemple 2: décodeur type 74LS138

## Library IEEE;

USE IEEE.std\_logic\_1164.all;

**ENTITY 74LS138 IS**

port (A, B, C, G2AN, G2BN, G1 : in std\_logic; YN : out std\_logic\_vector (7 downto 0)

END 74LS138;

**Remarque:** Souvent le type déclaré pour une entrée ou une sortie dépend de la manière dont on décrit l'architecture.

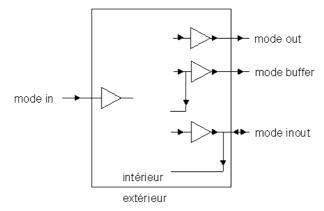

Le schéma ci-dessous illustre les différences obtenues selon les types de déclaration des ports.

Le mode **inout** est utilisé lorsqu'on a affaire à des lignes bidirectionnelles (cas des bus).

## 2.4) L'ARCHITECTURE

- Elle a pour rôle de décrire le **comportement** du composant VHDL. Elle correspond au **schéma électrique interne** du composant et est nécessairement associée à une entité.

- Toutes les instructions qui la composent sont exécutées de manière **concurrente** (ou simultanée).

- Les descriptions peuvent être comportementales ( elles ne font pas appel à des structures matérielles) ou structurelles ( netlist au niveau composant) ou mixtes ( un mélange des deux).

Syntaxe générale:

ARCHITECTURE <nom\_arch> OF <nom\_entité> IS

Zone de déclaration

BEGIN

Description de la structure logique

END <nom arch>;

Zone de déclaration:

Elle permet d'identifier des signaux, des constantes ainsi que leurs caractéristiques utilisés par l'architecture

exemple:

## signal sig Ut: integer range 0 to 9;

Après avoir créé dans l'**ENTITE** du composant les broches de sorties correspondant à Ut, on crée maintenant dans l'architecture le signal correspondant. Au signal sig\_U sera affectée, à l'intérieur du composant, une (des) **équipotentielle(s)**.

En général il est nécessaire de déclarer un signal lorsque celui-ci est utilisé comme une entrée dans une équation logique alors qu'il n'est pas une entrée du circuit (non déclaré dans la zone de **PORT**) : par exemple les sorties d'un compteur seront nécessairement des signaux puisque ils participent à la détermination des états du compteur.

## Description de la structure logique:

C'est une suite d'instructions concurrentes.

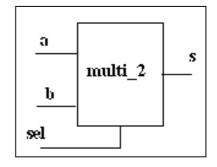

exemple 1: multiplexeur deux entrées a et b et une sortie s.

```

Library IEEE;

USE IEEE.std_logic_1164.all;

ENTITY multi_2 IS

Port (a, b, sel : in std_logic;

s : out std_logic

);

END multi_2;

```

ARCHITECTURE arch\_multi\_2 OF multi\_2 IS BEGIN

s <= (a AND NOT sel) OR (b AND sel); -- représentation structurelle

## END arch multi 2;

#### **OU ENCORE:**

```

s <= a WHEN sel = '0' ELSE

b; -- représentation comportementale

```

#### **OU ENCORE:**

```

WITH sel SELECT

s <= a WHEN '0',

b WHEN '1',

'0' WHEN OTHERS; -- autre représentation

```

## comportementale

## 2.5) MODELISATION DES ARCHITECTURES

## 2.5.1) Les SIGNAUX

Ils représentent des **équipotentielles enterrées** reliant différentes fonctions. Ils doivent obligatoirement être déclarés à l'intérieur de l'architecture. L'affectation du signal utilise le symbole : <=

exemple de déclaration:

```

SIGNAL sig_Drampe : std _logic_vector (5 downto 0); => génère 6 signaux : sig Drampe(5) à sig Drampe(0)

```

Initialisation du signal:

Il existe plusieurs possibilités:

```

- sig_Drampe <= "100111"; (on utilise les doubles cotes quand il y a plusieurs bits).</li>

- sig_Drampe <= X "27"; pour de l'hexa.</li>

```

Pour initialiser un bit (le 3 par ex.):

- sig Drampe(3) <= '0'; (on utilise les simples cotes quand il n'y a qu'un bit).

Attention !!! Les directives d'initialisation des signaux sont à utiliser avec précaution : ne pas oublier que l'objectif est la synthèse d'un circuit donc une réalisation matérielle. Préférer une phase d'initialisation qui opère sur l'apparition d'un signal réel (signal de reset, RAZ, ... par exemple).

#### 2.5.2) LES OPERATEURS

```

+, -, <, >, <=, >=, /=, *, / sont définis pour des entiers (type integer). AND, OR, NOT, XOR, & (concaténation) sont définis pour des bits.

```

## 2.5.3) AFFECTATION CONDITIONNELLE DES SIGNAUX

## Syntaxe:

```

nom_signal <= valeur_signal WHEN condition1 ELSE valeur_signal WHEN condition2 ELSE valeur_signal WHEN condition3 ELSE ..... valeur_signal;

```

## 2.5.4) AFFECTATION SELECTIVE DES SIGNAUX

#### Syntaxe:

WHEN OTHERS prend en compte toutes les combinaisons qui n'ont pas été décrites.

## 2.5.5) LE PROCESS

## 2.5.5.1) LES VARIABLES

Les variables font partie intégrante d'un process et doivent être déclarées à l'intérieur de celuici. Elles correspondent à un stockage temporaire.

Syntaxe:

```

VARIABLE <nom variable> := <type> := <valeur> ;

```

La variable est mise à jour immédiatement à l'intérieur d'un process alors que le signal est mis à jour à la fin d'un process.

## 2.5.5.2) SYNTAXE D'UN PROCESS

```

PROCESS (a,b)

BEGIN

```

liste des instructions

#### **END PROCESS:**

Remarque 1: le process ne s'exécute que si un évènement se produit sur a ou b. on appelle (a, b) la liste de sensibilité du process.

Remarque 2: Une architecture peut avoir plusieurs process. Ceux-ci s'exécutent

simultanément et les liens entre process sont effectués par les signaux.

Remarque 3: les instructions à l'intérieur d'un process sont séquentielles.

## 2.5.5.3) AFFECTATION DES SIGNAUX

Les affectations des signaux peuvent se faire à l'intérieur ou à l'extérieur du process. Elles ne prendront effet qu'à la fin de celui-ci.

## 2.5.5.4) INSTRUCTIONS SEQUENTIELLES

Le process permet au sein d'une architecture de décrire de manière séquentielle le comportement de fonctions. Il permet de faire appel à des instructions puissantes rencontrées dans les langages informatiques (C par exemple).

Instructions utilisables:

```

IF ...THEN...ELSE

FOR paramètre IN intervalle LOOP

CASE signal IS

WHEN valeur1 => instructions séquentielles;

WHEN valeur2 => instructions séquentielles;

END CASE;

2.5.6) EXEMPLES

2.5.6.1) INSTRUCTION IF ..THEN..ELSE: bascule D CD4013

library IEEE;

use IEEE.std logic 1164.all;

-- description des entités du CD4013

ENTITY CD4013 IS

(ck, d, s, r: in std logic;

port

q, qn: out std logic

);

END CD4013;

-- description de l'architecture

ARCHITECTURE arch CD4013 of CD4013 IS

SIGNAL sig q: std logic;

SIGNAL sig qn: std logic;

BEGIN

PROCESS (ck, r, s)

BEGIN

IF r='1' THEN

sig q \le 0';

ELSIF s = '1' THEN

sig q \leq 1';

ELSIF ck 'event and ck = '1' THEN

sig q \le d;

END IF;

sig_q = NOT sig_q;

END PROCESS;

q \le sig q;

qn \le sig qn;

```

```

END arch CD4013;

```

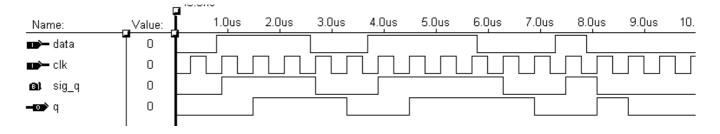

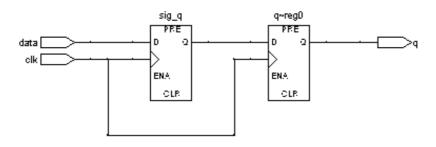

# **Bascule cd4013: MAUVAISE REPRESENTATION**

```

ENTITY cd4013b is

(clk, data: in std logic;

port

q: out std logic);

end cd4013b;

ARCHITECTURE arch cd4013b of cd4013b is

signal sig_q : std_logic;

begin

process (clk)

begin

if clk 'event and clk = '1' then

sig_q \le data;

-- un registre utilisé (affectation conditionnée par clk)

q \le sig_q;

-- un autre registre utilisé (affectation conditionnée par clk)

End if;

end process;

END arch cd4013b;

```

## 2.5.6.2) INSTRUCTION FOR...LOOP: Compteur CD 4040

```

library IEEE;

use IEEE.std_logic_1164.all;

-- description des entités du CD4040 (compteur 12 bits)

ENTITY CD4040 IS

port (clock, reset : in std_logic;

q : out std_logic_vector (11 downto 0)

);

END CD4040;

```

-- description de l'architecture

```

ARCHITECTURE arch CD4040 of CD4040 IS

SIGNAL sig q: std logic vector (11 downto 0);

BEGIN

PROCESS (clock, reset)

VARIABLE var q : std logic vector (11 downto 0);

VARIABLE carry: std logic;

BEGIN

IF reset = '1' THEN

sig q \le "000000000000";

ELSIF clock 'event and clock = '0' THEN

carry := '1';

FOR i in 0 to 11 LOOP

var q(i) := sig q(i) xor carry;

carry := sig q(i) and carry;

END LOOP;

END IF;

sig q \le var q;

END PROCESS;

q \le sig_q;

END arch CD4040;

autre façon de décrire ce composant:

library IEEE;

use IEEE.std logic 1164.all;

-- description des entités du CD4040 (compteur 12 bits)

ENTITY CD4040v1 IS

(clock, reset: in std logic;

q : out integer range 0 to 4095 -- on assimile la sortie à un entier

);

END CD4040v1;

-- description de l'architecture

ARCHITECTURE arch CD4040v1 of CD4040v1 IS

SIGNAL sig q: integer range 0 to 4095;

BEGIN

PROCESS (clock, reset)

BEGIN

IF reset = '1' THEN

sig q \le 0;

ELSIF clock 'event and clock = '0' THEN

sig q \le sig q + 1; -- on peut facilement faire une addition sur

-- des entiers

END IF;

END PROCESS;

q \le sig q;

END arch CD4040v1;

```

# 2.5.6.3. Utilisation d'un paramètre générique:

library IEEE;

Le paramètre générique permet de disposer d'un seul modèle pour un type de composant. Exemple : compteur modulo « modulo »

```

use IEEE.std_logic_1164.all;

-- description des entités du CD40xx (compteur n bits)

ENTITY CD40xxv2 IS

generic (modulo: integer:= 255);

(clock, reset: in std logic;

q : out integer range 0 to modulo

);

END CD40xxv2;

-- description de l'architecture

ARCHITECTURE arch CD40xxv2 of CD40xxv2 IS

SIGNAL sig_q : integer range 0 to modulo ;

BEGIN

PROCESS (clock, reset)

BEGIN

IF reset = '1' THEN

sig q \le 0;

ELSIF clock 'event and clock = '0' THEN

sig q \le sig q + 1;

END IF;

END PROCESS;

q \le sig q;

END arch CD40xxv2;

```

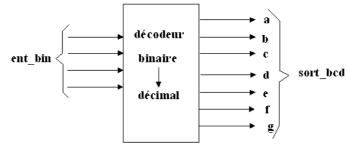

## 2.5.6.4) Instruction CASE: décodeur binaire -7 segments.

```

-- décodeur BCD - 7 segments

-- a b c d e f g

-- 0 1 2 3 4 5 6

```

library IEEE;

use IEEE.std logic 1164.all;

-- description des entités du décodeur

```

ENTITY decodeur IS

(ent bin: in std logic vector (3 downto 0);

port

sort bcd: out std logic vector (6 downto 0)

);

END decodeur;

description de l'architecture (sorties actives à 1)

ARCHITECTURE arch_decodeur of decodeur IS

BEGIN

PROCESS (ent bin)

BEGIN

CASE ent bin IS

-- ()

WHEN "0000" =>

sort bcd <= "0111111";

WHEN "0001" =>

sort bcd <= "0000110";

-- 1

sort bcd <= "1011011";

-- 2

WHEN "0010" =>

WHEN "0011" =>

sort bcd <= "1001111";

-- 3

WHEN "0100" =>

sort bcd <= "1100110";

-- 4

-- 5

WHEN "0101" =>

sort_bcd <= "1101101";

WHEN "0110" =>

sort bcd <= "1111101";

-- 6

WHEN "0111" =>

sort bcd <= "0000111";

-- 7

sort_bcd <= "1111111";

-- 8

WHEN "1000" =>

sort bcd <= "11011111";

-- 9

WHEN "1001" =>

WHEN others =>

sort bcd <= "0000000";

-- éteint

END CASE;

END PROCESS;

END arch decodeur;

2.5.6.5) Additionneur 4 bits

2.5.6.5.1) représentation structurelle

library IEEE;

use IEEE.std logic 1164.all;

-- description des entités de l'additionneur

ENTITY adder 4 IS

(a0,a1,a2,a3,b0,b1,b2,b3: in std logic;

s0,s1,s2,s3,s4 : out std logic

);

END adder 4;

-- description de l'architecture

ARCHITECTURE arch adder 4 of adder 4 IS

SIGNAL sig r0 : std logic;

SIGNAL sig r1 : std logic;

SIGNAL sig r2: std logic;

```

```

SIGNAL sig r3 : std logic;

BEGIN

s0 \le a0 \text{ XOR b0};

sig r0 \le a0 and b0;

s1 \le sig r0 xor a1 xor b1;

sig r1 \leq (a1 \text{ and } b1) \text{ or } (sig r0 \text{ and } (a1 \text{ or } b1));

s2 \le sig r1 xor a2 xor b2;

sig r2 \le (a2 \text{ and } b2) \text{ or } (sig r1 \text{ and } (a2 \text{ or } b2));

s3 \le sig r2 xor a3 xor b3;

sig r3 \le (a3 and b3) or (sig r2 and (a3 or b3));

s4 \le sig r3;

END arch adder 4;

2.5.6.5.2) Représentation par un process

library IEEE;

use IEEE.std_logic_1164.all;

-- description des entités de l'additionneur 2n entrées

ENTITY adder n IS

generic (n: integer := 8);

(a,b: in std logic vector (n downto 1);

s: out std logic vector (n downto 1);

r: out std logic

);

END adder n;

-- description de l'architecture

ARCHITECTURE arch adder n of adder n IS

SIGNAL sig s: std logic vector (n downto 1);

SIGNAL sig r: std logic;

BEGIN

PROCESS (a,b)

variable var s: std logic vector (n downto 1);

variable var r: std logic;

BEGIN

var r:='0';

for i in 1 to n loop

var s(i) = a(i) xor b(i) xor var r;

var r := (a(i) \text{ and } b(i)) \text{ or } (\text{var } r \text{ and } (a(i) \text{ or } b(i)));

end loop;

sig s \le var s;

sig r \le var r;

end process;

s \le sig s;

```

```

r \leq sig_r;

END arch_adder_n;

2.5.6.5.3) Additionneur n bits: représentation comportementale

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std logic arith.all;

-- description des entités de l'additionneur 2n entrées

ENTITY adder simple IS

generic (n: integer := 255);

(a,b: in integer range 0 to n;

s : out integer range 0 to 2*n

);

END adder_simple;

-- description de l'architecture

ARCHITECTURE arch adder simple of adder simple IS

BEGIN

s \leq a + b;

END arch_adder_simple;

```

# 3) La conception haut niveau

# 3.1) La conception hiérarchisée

On l'utilise lorsque le problème posé devient suffisamment complexe. On effectue une décomposition fonctionnelle du problème. On crée une entité pour chacune des fonctions identifiées (si elles sont différentes). On utilise l'instruction **PORT MAP** pour interconnecter les signaux et ports entre eux. Si une fonction est utilisée plusieurs fois (voir ci-dessous) on crée des instances de cette fonction.

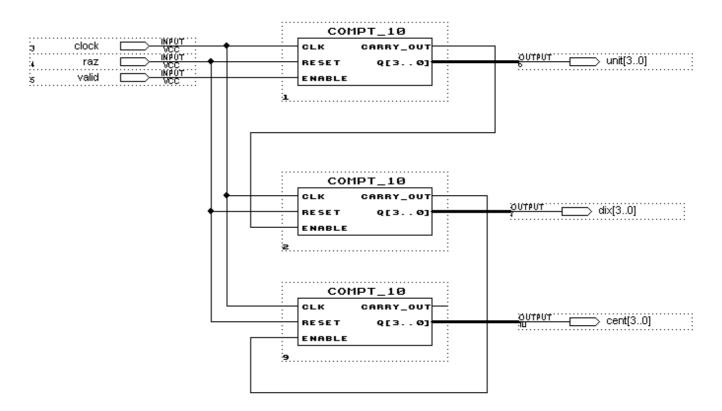

#### Exemple:

Soit à concevoir le circuit de comptage compt\_1000 (de 0 à 999) ci-dessous à partir de trois compteurs base 10 :

On décide de créer un compteur base 10 (compt\_10) qui sera mis en cascade. L'entité du fichier de description du circuit compt\_10 est représentée ci-dessous :

```

ENTITY compt_10 IS

PORT (clk, reset, enable: in std_logic;

carry_out: inout std_logic;

q: inout integer range 0 to 9);

END compt_10;

Le fichier VHDL du circuit compt_1000 est le suivant:

-- Compteur modulo 1000:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY compt_1000 IS

PORT (clock, raz, valid: IN std_logic;

unit, dix, cent: inout integer range 0 to 9);

```

```

END compt 1000;

ARCHITECTURE arch compt 1000 OF compt 1000 IS

signal cr dix, cr cent, cr mille: std logic;

component compt 10

PORT (clk, reset, enable: IN std logic;

carry out: inout std logic;

q: inout integer range 0 to 9);

end component;

BEGIN

U1: compt 10

-- U1 est une instance de compt 10

port map (clk => clock, reset=>raz, enable=>valid, carry out=>cr dix, q=>unit);

U2: compt 10

port map (clk => clock, reset=>raz, enable=>cr dix, carry out=>cr cent, q=>dix);

U3: compt 10

port map (clk => clock, reset=>raz, enable=>cr cent, carry out=>cr mille, q=>cent);

END arch compt 1000;

3.2) GENERICITE

Il est possible d'exploiter la généricité pour l'affectation des broches. Exemple sur l'additionneur :

Additionneur 2 mots de 1 bit add 1

library IEEE;

use IEEE.std_logic 1164.all;

ENTITY add 1 IS

port (A, B, Cin: in std logic;

S, Cout: out std logic

END add 1:

ARCHITECTURE arch add 1 of add 1 IS

BEGIN

S \le A XOR B XOR Cin;

Cout \leq (A and B) or (Cin and (A xor B));

END arch add 1;

Additionneur 8 bits generic adder sous forme générique utilisant add 1:

library IEEE;

use IEEE.std logic 1164.all;

entity generic adder is

generic( n: integer := 8);

port (

a,b: in std logic vector (n-1 downto 0);

ci : in std logic;

sum: out std logic vector (n-1 downto 0);

co : out std logic);

end entity;

architecture arch of generic adder is

```

```

signal C : std_logic_vector (n downto 0);

---

component add_1

port (A, B, Cin : in std_logic;

S, Cout : out std_logic);

end component;

---

begin

---

C(0) <= ci;

co <= C(n);

---

boucle: for I in 0 to n-1 generate

inst: add_1 port map (A(I), B(I), C(I), sum(I), C(I+1));

end generate boucle;

---

end arch;</pre>

```

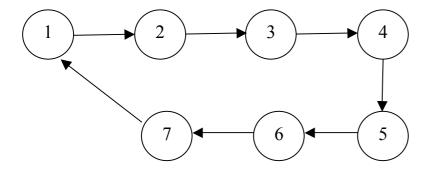

# 3.3) Synthèse des machines à états

(nota: Un seul état actif à tout instant):

Puisqu'un seul état est actif à tout instant, on peut utiliser une variable ou un signal de type **vector** ou **integer**. Si N est le nombre d'états de la machine, alors la taille du type **integer** sera N ou si c'est un type **vector** sa taille sera n de telle sorte que  $N \le 2^n$

Exemple : compteur synchrone modulo 7 (compte de 0 à 6) Graphe d'état (chaque transition est validée par un front d'horloge non représenté). Un signal de reset remet le circuit dans l'état 1 (non représenté).

| Etat | Q2 Q1 Q0 |  |  |  |

|------|----------|--|--|--|

| 1    | 000      |  |  |  |

| 2    | 001      |  |  |  |

| 3    | 010      |  |  |  |

| 4    | 011      |  |  |  |

| 5    | 100      |  |  |  |

| 6    | 101      |  |  |  |

| 7    | 110      |  |  |  |

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY compt_etat_7 IS

PORT (clk, reset : IN std_logic;

q0, q1, q2 : OUT std_logic);

END compt_etat_7;

ARCHITECTURE arch_compt_etat_7 OF compt_etat_7 IS

BEGIN

process (reset, clk)

variable etat : integer range 1 to 7;

```

```

begin

if reset ='1' then

etat := 1;

q0 \le '0'; q1 \le '0'; q2 \le '0';

elsif clk'event and clk='1' then

case etat is

when 1 =>

etat:=2;

q0<='1'; q1<='0'; q2<='0';

when 2 \Rightarrow

etat:=3:

q0<='0'; q1<='1'; q2<='0';

when 3 =>

etat:=4;

q0<='1'; q1<='1'; q2<='0';

when 4 =>

etat:=5;

q0 \le 0'; q1 \le 0'; q2 \le 1';

when 5 =>

etat:=6;

q0<='1'; q1<='0'; q2<='1';

when 6 =>

etat:=7;

q0<='0'; q1<='1'; q2<='1';

when others =>

etat :=1;

q0<='0'; q1<='0'; q2<='0';

end case;

end if;

end process;

END arch_compt_etat_7;

```

## Autre écriture possible :

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

```

```

ENTITY compt etat 7a IS

PORT (clk, reset

: IN std logic;

q0, q1, q2

: OUT std logic);

END compt etat 7a;

ARCHITECTURE arch compt etat 7a OF compt etat 7a IS

TYPE STATE_TYPE IS (e0,e1,e2,e3,e4,e5,e6);

signal etat: state type;

BEGIN

process (reset, clk)

begin

if reset ='1' then

etat \le e0;

elsif clk'event and clk='1' then

case etat is

when e0 =>

etat<=e1;

when e1 =>

etat \le e2;

when e2 =>

etat \le e3;

when e3 =>

etat<=e4:

when e4 =>

etat \le e5;

when e5 =>

etat<=e6;

when others =>

etat \le e0;

end case;

end if:

end process;

q0 <= '1' when etat=e1 or etat=e3 or etat=e5 else '0';

q1 <= '1' when etat=e2 or etat=e3 or etat=e6 else '0';

q2 <= '1' when etat=e4 or etat=e5 or etat=e6 else '0';

END arch compt etat 7a;

```

On peut noter que dans ce mode de représentation, on aura un délai supplémentaire entre l'élaboration des sorties et le front d'horloge (présence des portes OU après les bascules).

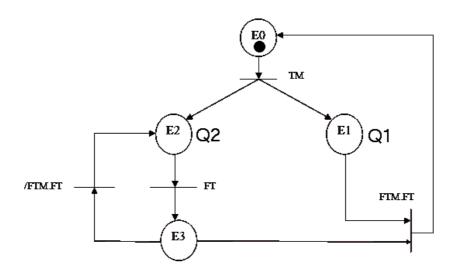

# 3.3) Synthèse des Réseaux de Petri :

Un réseau de Petri pouvant avoir plusieurs places marquées à tout instant, la solution la plus simple est d'associer un signal à chaque place. Dans ce cas les signaux seront nécessairement de type bit.

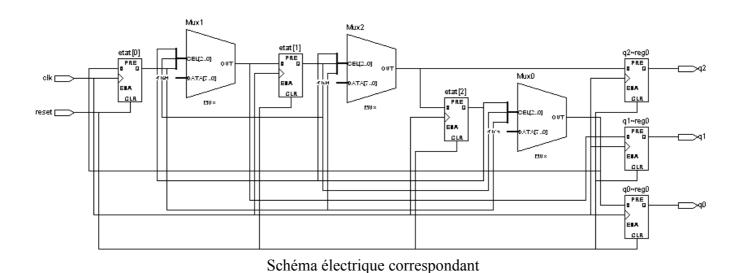

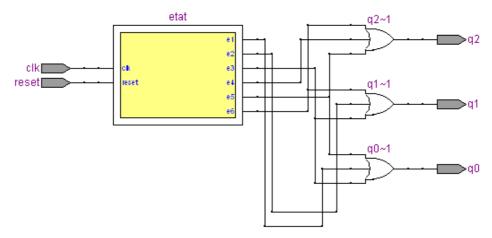

## Représentation VHDL du réseau ci-dessus :

(Nota : pour ne pas surcharger le réseau, les signaux de reset et clk n'apparaissent pas. « reset » remet le réseau dans sa configuration initiale : place E0 marquée).

```

ENTITY petri 1 IS

PORT (reset, clk, tm, ftm, ft: IN std logic;

q1, q2 : out std logic

);

END petri 1;

ARCHITECTURE arch petri 1 OF petri 1 IS

signal e0, e1, e2, e3 : std logic;

Begin

process (clk, reset)

begin

if reset='0' then

e0 <='1'; e1 <='0'; e2 <='0'; e3 <='0';

elsif clk'event and clk ='1' then

if e0 = '1' and tm = '1' then

e0 <='0'; e1 <='1'; e2 <='1';

end if:

if e2 = '1' and ft = '1' then

e3 <='1'; e2 <='0';

end if;

if (e1 and e3 and ftm and ft) ='1' then

e0 <='1'; e1 <='0'; e3 <='0';

end if;

if (e3 and ft and not ftm) = '1' then

e3 <='0'; e2 <='1';

end if;

end if;

```

```

end process; q1 \le e1; q2 \le e2; END arch petri 1;

```

## Quelques règles pour la conception d'un système complexe:

- 1) Privilégier une approche « Top-Down »

- identifier les fonctions principales et éventuellement les décomposer pour aboutir à des fonctions plus simples à concevoir

- identifier les entrées/sorties et les signaux d'interconnexion entre les différentes fonctions

- si les fonctions sont utilisées plusieurs fois, privilégier une approche « composant » sinon on peut associer à une fonction un « process »

- 2) Labelliser les fonctions, signaux et variables de manière claire afin de faciliter la phase de mise au point. Exemple :

- s\_fp1\_nom signal pour un signal généré par la fonction fp1 et actif à 1

- s\_fp1\_nom signal\_n pour un signal généré par la fonction fp1 et actif à 0

- v fp1 nom variable pour une variable interne à la fonction fp1

- 3) prévoir un signal de « remise à zéro » qui remet le circuit qui a été conçu dans une configuration connue (surtout si le circuit a un fonctionnement séquentiel)

- 4) valider chaque fonction séparément avant intégration dans le niveau supérieur (tests unitaires)

- 5) synchroniser les signaux d'entrée asynchrones/système pour éviter les aléas de fonctionnement

- 6) Enfin (le plus difficile!) penser « circuit » et surtout pas « programme informatique » sinon c'est l'échec assuré!