W

# Électronique Numérique

### Chapitre 3:

### Les convertisseurs

- Analogique-numérique (ADC ou CAN)

- Numérique-analogique (DAC ou CNA)

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

.

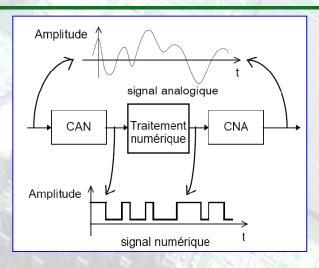

Les Convertisseurs Numérique-Analogiques et Analogique-Numériques :

### DAC/ADC: Généralités

### Avantages de la technique numérique (/analogique) :

- -Moins cher (conception, test, fabrication).

- -Beaucoup d'opérations de traitement du signal son plus facile à réaliser en numérique.

- -Moins sensible aux bruits.

- -L'implémentation numérique offre une meilleure flexibilité en permettant la programmation.

E

### CNA/CAN: Définitions

**Dynamique**: Variation possible de tension (ou de courant)

[de sortie pour un CNA / d'entrée pour un CAN]

Format: Format du mot binaire (S+M / C(2) / BCD/ ...)

**Résolution**: Plus petite tension manipulable (Dynamique/2<sup>n</sup>)

[confondu souvent avec le nombre de bit]

Cadence: Vitesse de conversion en «Sample Per Seconde» (SPS)

[peut être exprimé en MHz du signal d'entrée pour un CAN]

Précision : Différence entre la sortie théorique et effective

[exprimé en %, mv ou lsb]

Fidélité : Le fait de donner le même résultat pour une entrée donnée

Linéarité (erreur de) : différence entre la courbe idéale et effective

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

Les Convertisseurs Numérique-Analogiques et Analogique-Numériques :

### CNA/CAN (doc. Technique de l'ingénieur)

#### Evolutions du marché des CAN et CNA

#### Tableau 1 - Les neufs premiers fabricants de CAN et CNA en 2001

| Place                | Société                      | Chiffre<br>d'affaires 2001<br>pour la<br>conversion<br>(millions de \$) | Part<br>de<br>marché<br>(%) |

|----------------------|------------------------------|-------------------------------------------------------------------------|-----------------------------|

| 1                    | Analog Devices (ADi)         | 465                                                                     | 33                          |

| 2                    | Texas Instruments (TI)       | 200                                                                     | 14                          |

| 3                    | Maxim                        | 154                                                                     | 11                          |

| 4                    | Philips                      | 95                                                                      | 7                           |

| 5                    | National Semiconductor (NSC) | 55                                                                      | 4                           |

| 6                    | MicroChip                    | 50                                                                      | 4                           |

| 7                    | Intersil                     | 50                                                                      | 4                           |

| 8                    | Hitachi                      | 39                                                                      | 3                           |

| 9                    | Sony                         | 33                                                                      | 2                           |

| Total des 9 sociétés |                              | 1 141                                                                   | 82                          |

| Total marché         |                              | ≈ 1 400                                                                 | 100                         |

# Les Convertisseurs Numérique-Analogiques

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

Ę

LINEL

#### Les Convertisseurs Numérique-Analogiques :

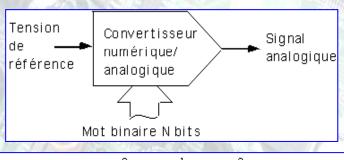

### Généralités et Principes

$$\mathbf{U_{out}} = \mathbf{U_{r\acute{e}f}} \cdot \frac{\mathbf{A_{0} \cdot 2^{0} + A_{1} \cdot 2^{1} + A_{2} \cdot 2^{2} + ... + A_{n-1} \cdot 2^{n-1}}}{2^{n} - 1}$$

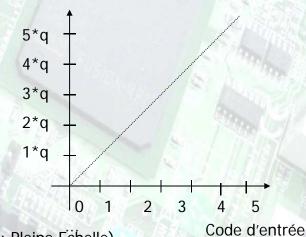

Vout = N.q

Tension de sortie

U<sub>ref</sub> correspond à la pleine dynamique ( ou PE : Pleine Echelle).

U<sub>ref</sub> /(2<sup>n</sup>-1) est aussi appelée quantum (q) ou lsb

빌

# CNA (compléments)

- Nombre de bits : n; nb de valeurs entières distinctes :  $2^n$ ; nb d'intervalles :  $2^n 1$

- Pleine échelle (full scale) : Mode unipolaire : PE (FS) = V<sub>max</sub>

$\label{eq:max_var} \mbox{Mode bipolaire : PE} \ (FS) = V_{\rm mix} - V_{\rm min} \\ \mbox{ce demicr cas, cn général } V_{\rm min} = V_{\rm max} \ , \ \mbox{ct est appelé "décalage en tension"} \ (\textit{offset}).$

- Sortie analogique : sortie en tension : le CNA est un générateur de Thévenin - sortie en courant : le CNA est un générateur de Norton

- Notations (exemple pour n = 8 bits):

$$V_5 = \frac{10}{255} \left( 2^7 D_7 + 2^6 D_6 + ... + 2 D_1 + D_0 \right) = \frac{PE}{2^n - 1} \sum_{i=0}^{n-1} 2^i D_i$$

$$V_{5} = 10 \frac{256}{255} \left( \frac{D_{7}}{2} + \frac{D_{6}}{4} + \dots - \frac{D_{1}}{128} + \frac{D_{0}}{256} \right) = PE \frac{2^{n}}{2^{n} - 1} \sum_{i=1}^{n} \frac{D_{n-i}}{2^{i}}$$

Thierry Perisse perisse@cict.fr U.P.S. Toulouse Chap 3

Les Convertisseurs Numérique-Analogiques :

# Quelques Architectures de CNA

DAC (CNA) Potentiométrique (à diviseur de tension);

DAC (CNA) à somme pondérées;

DAC (CNA) à réseau R/2R;

DAC ...

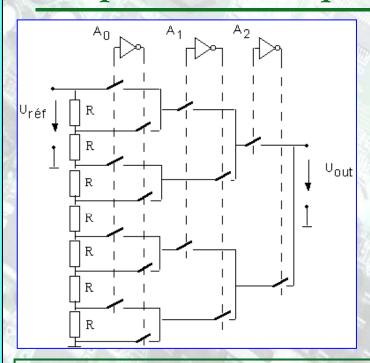

### CNA potentiométrique (à diviseur de tension)

**Principe**: On choisi parmi 2<sup>n</sup> tension celle que l'on veut.

**Rmque**: Toutes les valeurs possibles (2<sup>n</sup>) sont fabriquées par le diviseur potentiométrique.

Choix de la sortie par multiplexage (1 parmi 2<sup>n</sup>).

#### Inconvénients :

Echelle de résistance. Nb Interrupteurs.

EX: Donner l'expression de Vout=f(Vref) pour les codes suivants 000 001 101? En déduire l'expression générale de Vout =f(Vref,A0,A1,A2)?

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

LINEL

Electronique Numérique

Les Convertisseurs Numérique-Analogiques

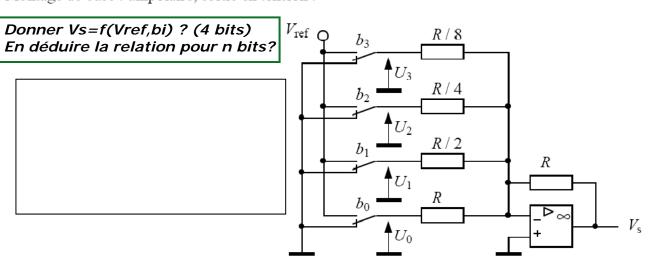

# Ex: CNA (4 bits) à résistances pondérées

CNA à résistances pondérées

Montage de base : unipolaire, sortie en tension :

Inconvénients de ce montage :

pas réalisable en valeurs normalisées sensibles aux tolérances pas intégrables pas d'appariement possible

Electronique Numérique

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

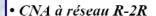

# CNA (4 bits) à réseau R-2R

Montage de base : unipolaire, sortie en courant :

Hyp: Le point A est une masse virtuelle.

Donner l'équation de Is=f(Vref,R,bi) ? (pour 4 bits)

En déduire la relation pour n bits?

Proposer un montage permettant de convertir Is en une tension Vs.

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

11

W/10 77 9

Electronique Numérique

빌

LINEL

Les Convertisseurs Numérique-Analogiques

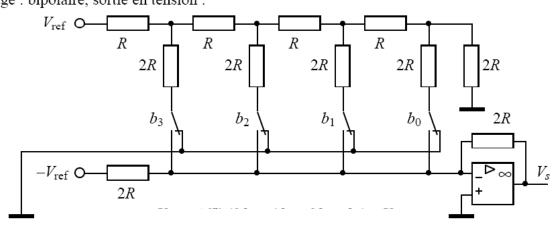

### CNA (4 bits) à réseau R-2R

- Autre montage : bipolaire, sortie en tension :

Donner l'équation de Vs=f(Vref,R,bi) ? (4 bits) En déduire la relation pour n bits ?

Les Convertisseurs Numérique-Analogiques : LINE Les erreurs systématiques sortie Réponse réelle sortie Réponse réelle analogique analogique analogique Réponse Réponse idéale idéale ent rée Offset 2.44 mV numérique numérique Erreur de gain : Eg Courbe idéale Erreur d'offset : Eo à erreur d'offset nulle Performances de CNA disponibles sur le marché Etat de l'art des CNA sur le marché Estimation de prix Référence commerciale N bits Architecture Technologie Boîtier **Fabricant** Electronique Numérique 2×24 46 kHz **CMOS** 2 64 20 VOFN PCM1772 2 x 24 196 kHz CMOS 200 28 SSOP AD1955 16 100 MHz Parallèle 4 × interp. CMOS 80 860 64 QFP MB86060 12 400 MHz Parallèle CMOS 80 300 80 LQFP MB86061 14 250 MHz Parallèle **CMOS** Non communiqué 54 Fabless (1) Fabless (1)

Chap 3

14

300 MHz

Parallèle

Parallèle

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

CMOS

40

115

20

48 PQFP

28 QSOP

AD9755

MAX 5182

TI

AD

Fujitsu

Fujitsu

Impinj

AD

Maxim

Еg

빌

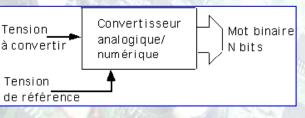

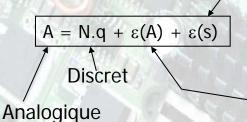

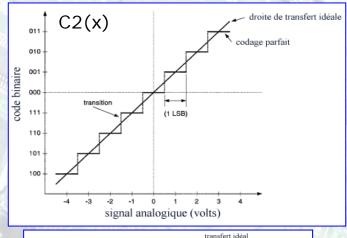

# Les convertisseurs Analogique-Numériques

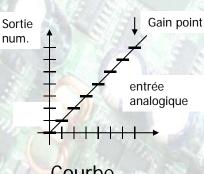

# Généralités et Principes (1)

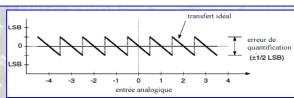

Imperfections

La courbe peut être définie par troncature ou par arrondi (1/2.q d'offset)

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

15

NEL

Les Convertisseurs Analogique-Numériques :

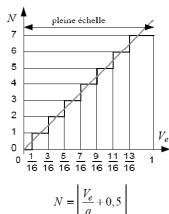

# Généralités et Principes (2)

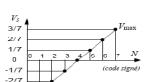

- Pleine échelle (full scale) : Mode unipolaire : PE (FS) =  $V_{\rm max}$  Mode bipolaire : PE (FS) =  $V_{\rm max}$   $V_{\rm min}$

- *Résolution* ou "pas de quantification" ou "incrément" :  $\Delta V_e = q = \frac{\text{PE}}{2^n}$

- • Caractéristique (avec N arrondi à l'entier le plus proche) : unipolaire : bipolaire :

$$N = \left\lfloor \frac{V_e - V_{\min}}{q} + 0.5 \right\rfloor$$

빌

### Quelques Architectures de CAN

Architecture semi-flash

Architecture à double rampe analogique

Architecture à rampe numérique

Architecture à approximation successives

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

17

7.4

Les Convertisseurs Analogique-Numériques :

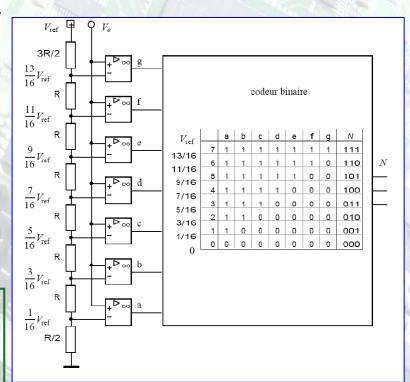

### CAN // à comparateurs (Architecture flash)

### Exemple d'un CAN 3 bits :

### Principe:

Fabriquer  $2^{n}$ -1 seuils à l'aide d'une tension Vref et de  $2^{n}$  résistances; Comparer Ve à ces seuils.

#### Avantages :

Le plus rapide des CAN(ADC).

#### Inconvénients :

Nombre de comparateurs (2<sup>n</sup>-1). si 10 bits → 1023 Comparateurs!! Nb et qualité des résistances (2<sup>n</sup>). si 10 bits → 1024 Résistances!!

#### Exercice:

Donner la valeur de N pour une entrée analogique Ve de 3v. avec Vref=10v.

Chap 3

Electronique Numérique

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

I NEI

Electronique Numérique

LINEL

Les Convertisseurs Analogique-Numériques :

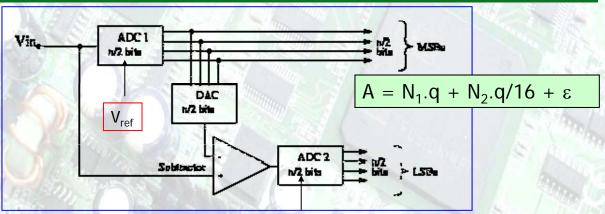

### Architecture semi-flash

### Principe:

Utiliser des ADC flash n/2 bits et un ADC. Le deuxième ADC converti le résidu.

#### Avantages :

Reste rapide  $(2.T_{ADC}+T_{DAC})$

#### Inconvénients :

Reste compliqué en matériel

Chap 3

$V_{ref}/16$

#### Ex: Pour un CAN semi-flash de 8bits:

- Donner le nombre de comparateurs ?

- Combien de comparateurs a-t-on économisé par rapport à l'architecture Flash?

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

Les Convertisseurs Analogique-Numériques :

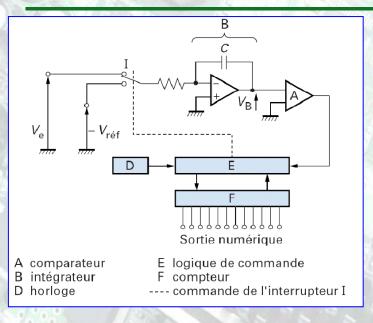

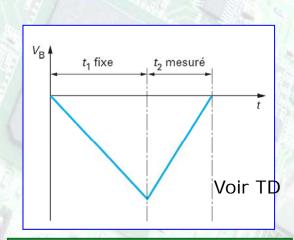

# Architecture à double rampe analogique

Charger une capa avec Ve (t1 fixe) et la décharger avec -Vref (mesure de t2).

#### Exercice:

Donner les équations de  $V_{\scriptscriptstyle R}(t)$

- pour Ve en entrée.

- puis pour Vref.

Donner la relation entre Ve d'une part et Vref, t1 et t2 d'autre part.

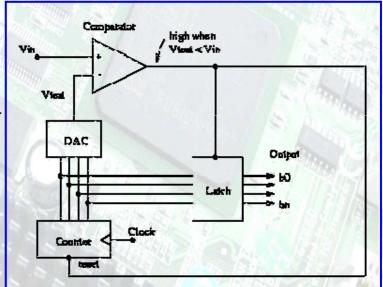

### Architecture à rampe numérique

### Principe:

Compter linéairement, faire la conversion NA de cette suite et la comparer avec Vin.

Ouand Vtest>Vin => Arrêt conversion.

#### Avantages :

Plus d'in fluence I, C Résolution quelconque

#### Inconvénients :

Lent à très lent (qq ms /qq sec) DAC n bits

Temps de conversion dépend de Vin

Voir TD

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

Les Convertisseurs Analogique-Numériques :

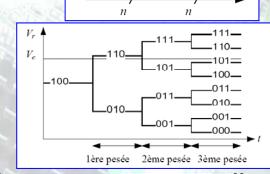

### Architecture à approximation successives

### Principe:

Le convertisseur compare la tension d'entrée Ve avec la sortie d'un CNA par pesées successives, comme le ferait une balance. La technique consiste à procéder par dichotomie, en divisant successivement par deux l'intervalle de tension dans lequel est mesurée Ve.

Au départ, le bit de poids fort (MSB) est positionné à 1, les autres bits sont à 0.

Par exemple, pour n = 8, le mot test N = 1000 0000est envoyé au CNA, qui fournit la tension Vr:

- si Vr > Ve, le MSB est mis à 0, et le bit suivant est positionné à 1 : on envoie N = 0100 0000 dans le CNA.

-si Vr < Ve , le MSB ne change pas, et l'on envoie N = 1100 0000 dans le CNA.Etc...

Cet algorithme est réalisé dans un "registre à approximations successives" (Successive Approximation Register ou SAR).

logique de commande

registe à

approximations

successives

Chap 3

Electronique Numérique

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

当

### Architecture à approximation successives

#### Avantages :

Meilleur compromis vitesse/résolution

Temps de conversion : il faut *n* passes pour exécuter l'algorithme de dichotomie. L'intérêt de ce montage est que le temps de conversion est constant, et relativement faible.

Exercice: Représenter, en fonction du temps, le signal de sortie Vr du CNA de la chaîne de retour d'un CAN à approximations successives de 3 bits, PE=10v., travaillant en binaire naturel, lorsque la tension à convertir est Ve=4,5v.

Quel est le résultat de la conversion?

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

22

NEL

Les Convertisseurs Analogique-Numériques :

# Les erreurs systématiques

Courbe idéale

Erreur d'offset : Eo

Erreur de gain :

Eg

à erreur d'offset nulle

### Remarques:

- Les erreurs de non-linéarité intégrale et les erreurs de non-linéarité différentielle ne seront pas abordés dans ce chapitre.

- les erreurs peuvent être exprimées en % de la pleine échelle, en millivolt, en fraction de lsb.

- Il existe des procédures de réglage d'offstet (N=0) et de réglage de gain (N=Nmax).

Les Convertisseurs Analogique-Numériques :

# Doc. Technique de l'Ingénieur

| N bits | Fréquence | Architecture | Technologie    | Estimation<br>de prix<br>(€) | Consommation (mW) | Boîtier   | Référence<br>commerciale | Fabricant                       |

|--------|-----------|--------------|----------------|------------------------------|-------------------|-----------|--------------------------|---------------------------------|

| 2×24   | 96 kHz    | ΣΔ           | CMOS           | 5                            | 300               | 28 TSSOP  | AD1871                   | Analog Devices                  |

| 18     | 800 kHz   | SAR          | CMOS           | 30                           | 100               | 46 LFCSP  | AD7679                   | Analog Devices                  |

| 16     | 5 MHz     | Pipeline     | CMOS           | 35                           | 500               | 44 LQFP   | SPT8100                  | Signal Processing<br>Technology |

| 14     | 65 MHz    | Pipeline     | CMOS           | 35                           | 500               | 48 PQFP   | AD9244                   | Analog Devices                  |

| 12     | 210 MHz   | Pipeline     | BiCMOS         | 80                           | 1 300             | 100 TQFP  | AD9430                   | Analog Devices                  |

| 14     | 105 MHz   | Pipeline     | Bipolaire      | 50                           | 1 500             | 48 PQFP   | AD6645                   | Analog Devices                  |

| 8      | 1,5 GHz   | Flash        | Bipolaire SiGe | 500                          | 5 000             | 192 ESBGA | MAX 108                  | Maxim                           |

| 10     | 2 GHz     | NC (1)       | Bipolaire SiGe | NC (1)                       | 4 600             | CBGA152   | TS83102                  | ATMEL                           |

Etat de l'art des CAN sur le marché

Electronique Numérique

LINEL

Les Convertisseurs Analogique-Numériques :

# Doc. Technique de l'Ingénieur

| Tableau 4 – Performances des produits commerciaux usuels ou standards |              |                      |                                                                                                                                                                                                                                                                 |  |  |  |

|-----------------------------------------------------------------------|--------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Architecture                                                          | Résolution   | Vitesse (1)          | Avantages/Inconvénients                                                                                                                                                                                                                                         |  |  |  |

| Intégration                                                           | 8 à 18 bits  | ≤ 30 kSPS            | <ul> <li>+ Résolution élevée</li> <li>+ Faible consommation</li> <li>+ Excellente réjection analogique du bruit</li> <li>- Très faible vitesse d'échantillonnage</li> </ul>                                                                                     |  |  |  |

| SAR                                                                   | 8 à 16 bits  | ≤ 3 MSPS             | + Résolution élevée et précision<br>+ Faible consommation<br>- Vitesse d'échantillonnage limitée                                                                                                                                                                |  |  |  |

| ΣΔ                                                                    | 16 à 24 bits | ≤ 3 MSPS             | <ul> <li>+ Résolution la plus élevée et précision</li> <li>+ Excellente linéarité</li> <li>+ Faible consommation</li> <li>+ Excellente réjection numérique du bruit</li> <li>+ Adaptabilité potentielle</li> <li>- Vitesse d'échantillonnage limitée</li> </ul> |  |  |  |

| Pipeline subranging                                                   | 8 à 16 bits  | entre 10 et 400 MSPS | + Très rapide<br>+ Correction digitale des erreurs<br>+ Meilleur compromis vitesse résolution                                                                                                                                                                   |  |  |  |

| Flash                                                                 | 6 à 8 bits   | entre 1 et 20 GSPS   | + Les plus rapides - Résolution limitée - Puce de dimension importante - Capacité de l'entrée élevée - Forte consommation - Codes erratiques                                                                                                                    |  |  |  |

Chap 3

Thierry Perisse perisse@cict.fr U.P.S. Toulouse

27