# Electronique numérique LIE CNED 2<sup>eme</sup> année. Analyse et synthèse des systèmes séquentiels

Frédéric LECOMTE, Luc MUSEUR

Université Paris 13, Institut Galilée.

| Chapit      | re 1                                                                 | 5  |

|-------------|----------------------------------------------------------------------|----|

| Introductio | n                                                                    | 5  |

| 1.1. U      | n peu de vocabulaire                                                 | 5  |

| 1.2. C      | ù trouve-t-on des automates?                                         | 5  |

| 1.3. U      | n 1 <sup>er</sup> exemple d'automate : La commande d'un monte charge | 5  |

| 1.3.1.      | Le cahier des charges.                                               | 6  |

| 1.3.2.      | Le diagramme d'états                                                 | 6  |

| 1.4. L      | a conception des circuits numériques                                 | 7  |

| 1.4.1.      | Structure générale des automates                                     | 7  |

| 1.4.2.      | Réalisation physique des automates.                                  | 8  |

| Chapit      | re 2                                                                 | 10 |

| Analyse de  | es systèmes séquentiels                                              | 10 |

| 2.1. N      | lodélisation des systèmes séquentiels asynchrones                    | 10 |

| 2.1.1.      | Retour sur les systèmes combinatoires et séquentiels                 | 10 |

| 2.1.2.      | Un modèle de système séquentiel pour les circuits asynchrones        | 11 |

| 2.1.3.      | Etat présent, état futur                                             | 12 |

| 2.1.4.      | Un exemple simple : la bascule RS.                                   | 12 |

| 2.1.5.      | Deuxième exemple : l'astable                                         | 14 |

| 2.1.6.      | Conclusion pour les circuits asynchrones                             | 15 |

| 2.2. N      | lodélisation des systèmes synchrones                                 | 15 |

| 2.2.1.      | Systèmes synchrones avec horloge.                                    | 15 |

| 2.2.2.      | Evolution temporelle des systèmes synchrones                         | 16 |

| 2.3. A      | nalyse fonctionnelle des systèmes séquentiels                        | 17 |

| 2.3.1.      | Les différentes étapes.                                              | 17 |

| 2.3.2.      | Analyse d'un système asynchrone.                                     | 20 |

| 2.3.3.      | Analyse d'un système synchrone (1er exemple)                         | 23 |

| 2.3.4.      | Analyse d'un système synchrone (2 <sup>eme</sup> exemple)            | 26 |

| 2.3.5.      | Comparaison des deux circuits synchrones analysés                    | 29 |

| 2.4. lr     | térêt des circuits synchrones avec horloge                           | 30 |

| 2.4.1.      | Notion de course critique : aléas                                    | 30 |

| 2.4.2.      | Le rôle de l'horloge.                                                | 31 |

| 2.5.    | Ana                                                        | llyse temporelle des systèmes séquentiels                 | 31  |

|---------|------------------------------------------------------------|-----------------------------------------------------------|-----|

| 2.      | 2.5.1. Contraintes temporelles sur les bascules synchrones |                                                           | 31  |

| 2.      | 5.2.                                                       | Analyse temporelle d'un circuit                           | 33  |

| 2.      | 5.3.                                                       | Exemple du compteur                                       | 35  |

| 2.      | 5.4.                                                       | Remarques                                                 | 36  |

| 2.6.    | Exe                                                        | rcices corrigés                                           | 38  |

| 2.7.    | Exe                                                        | rcices supplémentaires                                    | 68  |

| Ch      | apitre                                                     | 3                                                         | 70  |

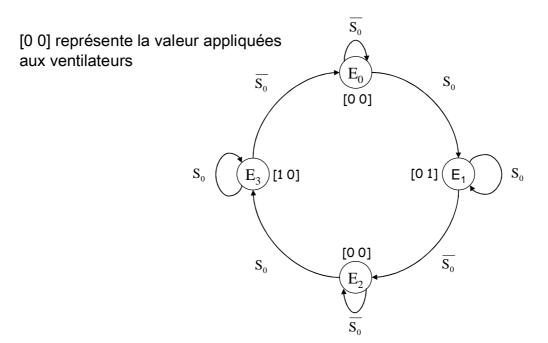

| Synthè  | se de                                                      | s systèmes séquentiels synchrones                         | 70  |

| 3.1.    | Prin                                                       | cipe de la synthèse                                       | 70  |

| 3.      | 1.1.                                                       | La méthode                                                | 70  |

| 3.      | 1.2.                                                       | Retour sur le compteur.                                   | 71  |

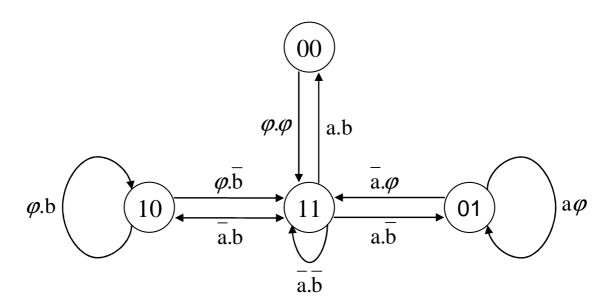

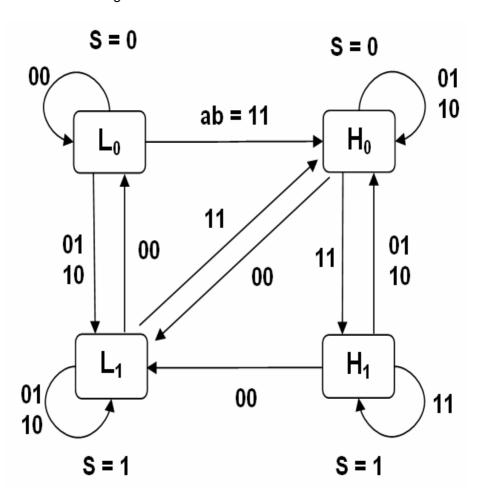

| 3.2.    | Les                                                        | diagrammes de transitions                                 | 75  |

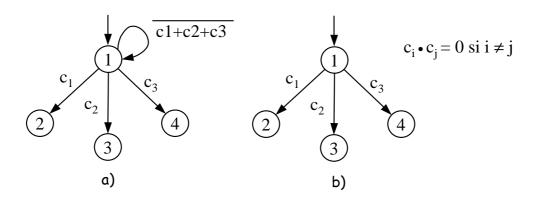

| 3.2     | 2.1.                                                       | Les règles importantes.                                   | 76  |

| 3.2     | 2.2.                                                       | Les états inutilisés (états parasites)                    | 77  |

| 3.2     | 2.3.                                                       | Simplification du diagramme d'états.                      | 80  |

| 3.3.    | Cor                                                        | nception des automates                                    | 82  |

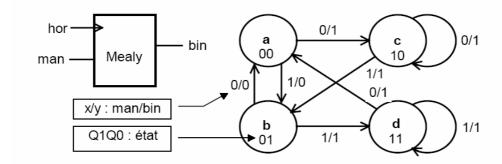

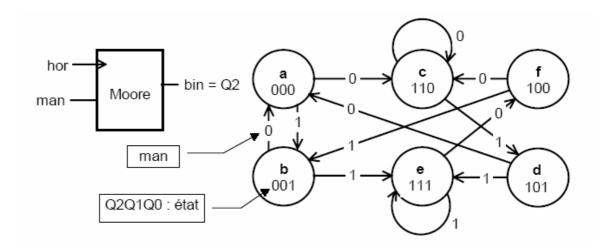

| 3.3     | 3.1.                                                       | Architecture des sorties : machines de Mealy et de Moore  | 82  |

| 3.3     | 3.2.                                                       | Exemple de machine de Moore                               | 83  |

| 3.3     | 3.3.                                                       | Exemple machine de Mealy                                  | 87  |

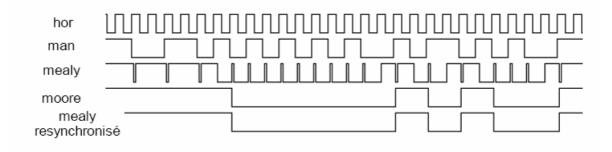

| 3.3     | 3.4.                                                       | Avantages et inconvénients des deux types d'architectures | 92  |

| 3.3     | 3.5.                                                       | Choix du codage.                                          | 92  |

| 3.4.    | Exe                                                        | rcices corrigés                                           | 96  |

| 3.5.    | Exe                                                        | rcices supplémentaires.                                   | 150 |

| Ch      | apitre                                                     | 4                                                         | 153 |

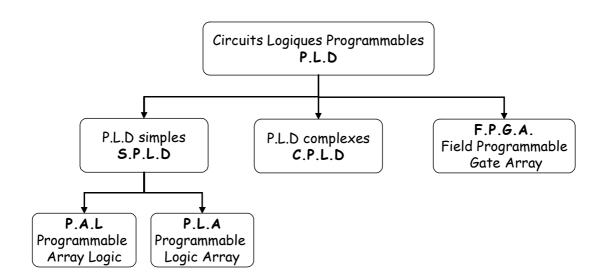

| Circuit | s logic                                                    | ques programmables                                        | 153 |

| 4.1.    | Intro                                                      | oduction                                                  | 153 |

| 4.2.    | Les                                                        | circuits logiques programmables simples SPLD              | 154 |

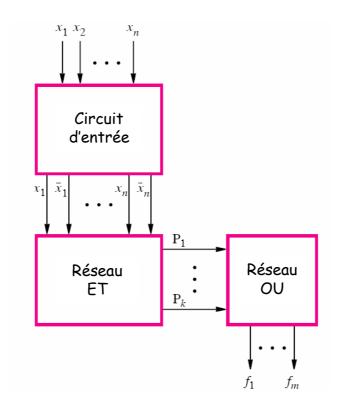

| 4.2     | 2.1.                                                       | Structure générale des SPLD                               | 154 |

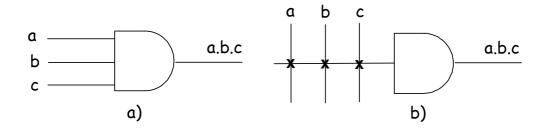

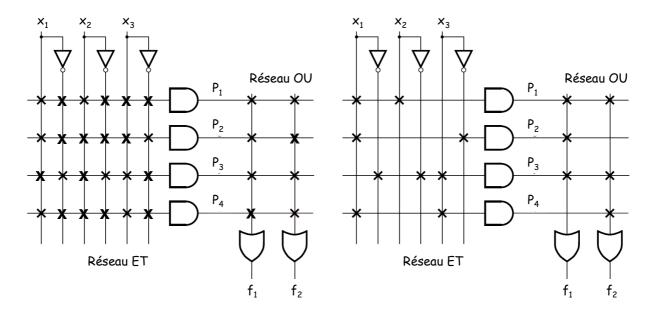

| 4.2     | 2.2.                                                       | Les Programmable Logic Array PLA                          | 155 |

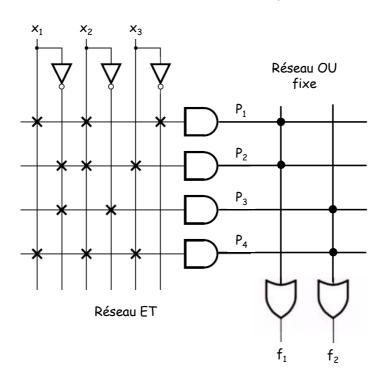

| 4.2     | 2.3.                                                       | Les Programmable Array Logic PAL                          | 158 |

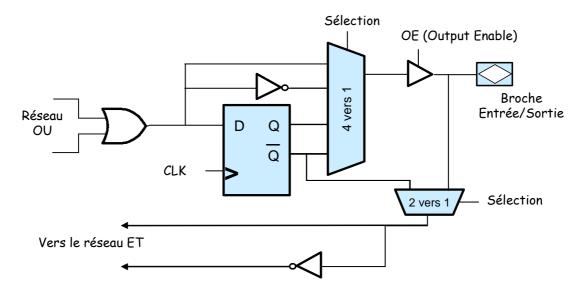

| 4 '     | 2.4                                                        | La structure de sortie                                    | 150 |

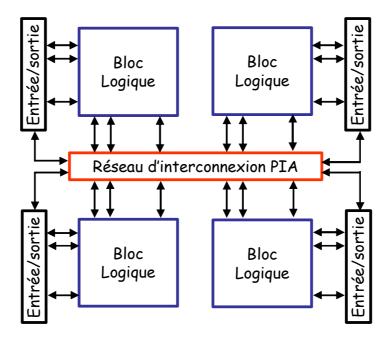

| 4.3. | Les | Complex Programmable Logic Device (CPLD)       | 161 |

|------|-----|------------------------------------------------|-----|

| 4.4. | Les | circuits Field Programmable Gate Array (FPGA). | 162 |

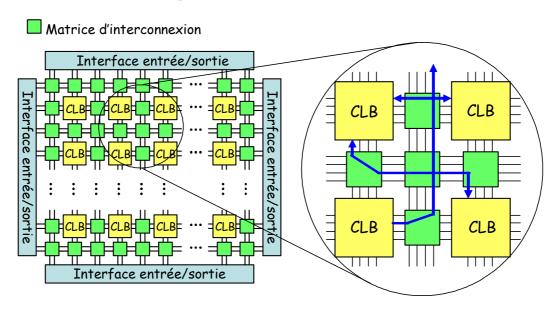

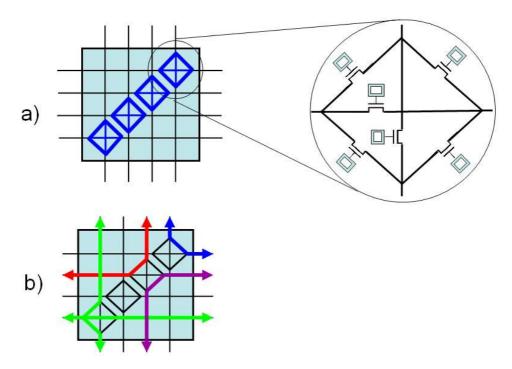

| 4.4  | .1. | Architecture générale.                         | 162 |

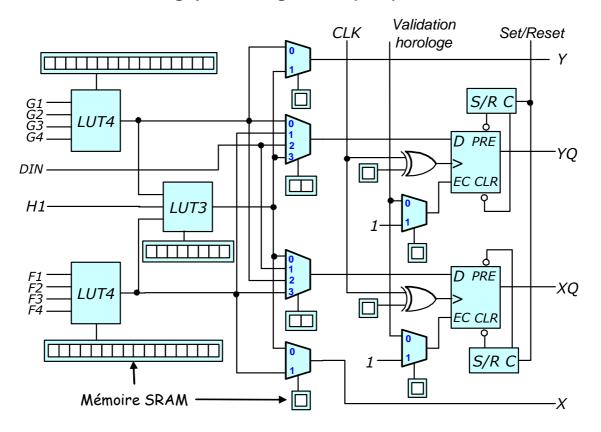

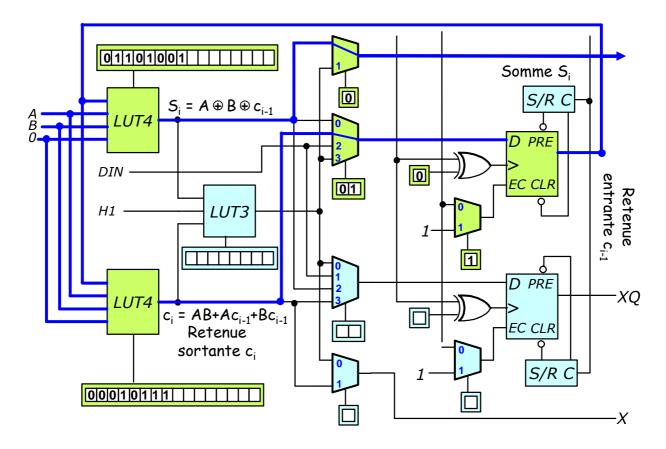

| 4.4  | .2. | Les Blocs Logiques Configurables (CLB).        | 163 |

| 4.4  | .3. | Les matrices d'interconnexion.                 | 165 |

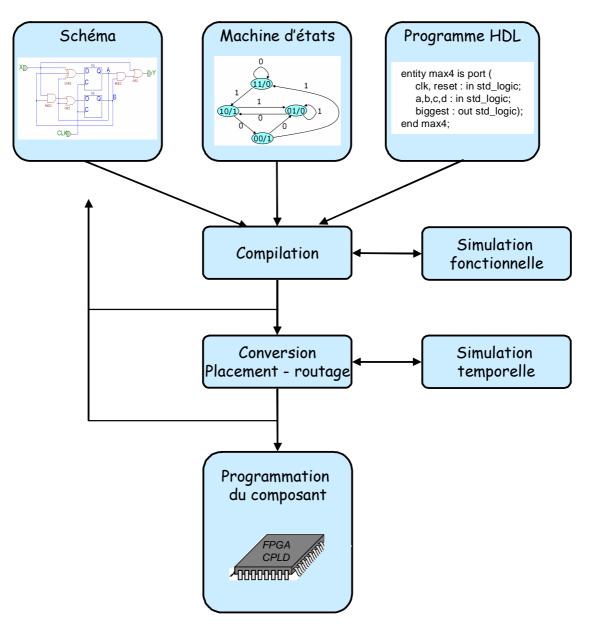

| 4.5. | Les | outils de développement                        | 167 |

| 4.6. | Con | clusion                                        | 168 |

# **Chapitre 1**

# Introduction

#### 1.1. Un peu de vocabulaire.

Les automates que nous allons étudier dans ce cours n'ont qu'un rapport très éloigné avec les machines mécaniques fabriquées depuis le 17 siècle ; ce sont des objets abstraits dont le nom varie selon les domaines dans lesquels ils sont utilisés. Les automaticiens parlent d'automates finis, les concepteurs de circuits numériques de machines à nombres finis d'états et les concepteurs d'unités centrales d'ordinateurs de séquenceurs.

#### 1.2. Où trouve-t-on des automates?

A peu près partout, la plus part des systèmes de commandes sont des automates. On peut citer, par exemple, de façon assez évidente :

Le système de commande d'un ascenseur.

Le système de régulation des feux à un carrefour

Le digicode contrôlant l'ouverture d'une porte

On utilise des automates dans tous les systèmes dont le fonctionnement peut être décrit par une chronologie faisant intervenir un nombre fini d'opérations distinctes conditionnées par des entrées extérieures. Les applications typiques sont :

La gestion d'un processus.

L'utilisation et/ou le partage d'une ressource.

Le traitement de données.

# 1.3. Un 1<sup>er</sup> exemple d'automate : La commande d'un monte charge.

#### 1.3.1. Le cahier des charges.

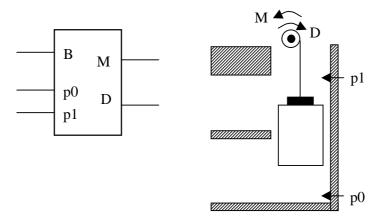

On considère un monte charge effectuant la liaison entre les 2 niveaux d'un bâtiment (figure 1). Le moteur est commandé par 2 signaux M (pour monter) et D (pour descendre). Ces commandes sont élaborées à partir des entrées :

B: bouton poussoir (B=1 si le bouton est enfoncé)

p0 et p1: détecteurs de position aux niveaux 0 et 1 (pi=1 si le monte charge est présent au niveau i)

Le fonctionnement du système est décrit par le cahier des charges suivant :

- **1.** Quand la cabine est à un étage si *B* est inactif elle s'arrête, si *B* est actif elle change d'étage.

- 2. Quand la cabine est entre 2 étages la dernière commande (*M* ou *D*) est maintenue.

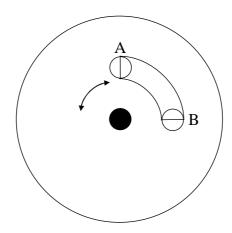

figure 1

#### 1.3.2. Le diagramme d'états.

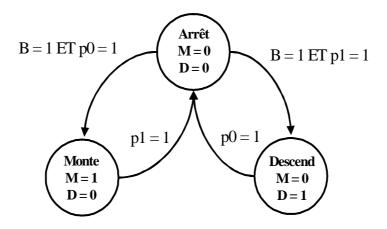

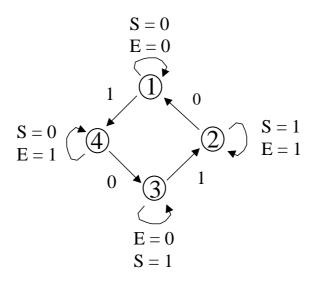

Le fonctionnement du monte charge peut être décrit sous la forme d'un diagramme (figure 2), que l'on appelle diagramme d'états<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>En automatique on utilise une approche semblable et les diagrammes d'états s'appellent des GRAFCET

figure 2

On retrouve sur ce diagramme les principes importants des automates :

- 1. La solution du problème est décrite sous forme d'étapes bien définies et bien séparées les unes des autres.

- 2. Chaque étape est représentée par un ensemble fini de valeurs que l'on appelle l'état interne de l'automate Cet état est physiquement matérialisé par les valeurs contenues dans une mémoire. Attention cette mémoire représente l'état de l'automate et non celui du système commandé. Dans l'exemple du monte charge, aucun des états n'indique la position de la cabine.

- 3. Les entrées du système provoquent des transitions entre les états. Une transition n'est réalisée que si le système est dans l'état de départ de la transition considérée et que la ou les conditions extérieures sont vérifiées.

- 4. Si aucune des transitions issues d'un état n'est active, toutes les conditions étant fausses, alors le système reste dans l'état considéré. Par défaut il y a mémorisation de l'état présent.

# 1.4. La conception des circuits numériques.

#### 1.4.1. Structure générale des automates.

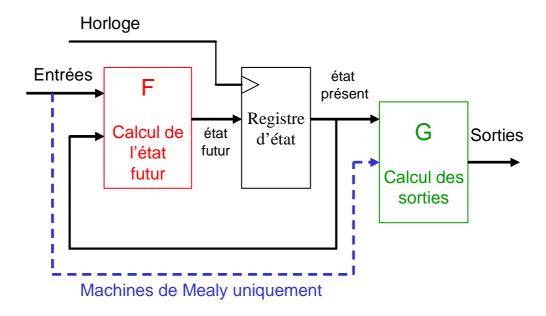

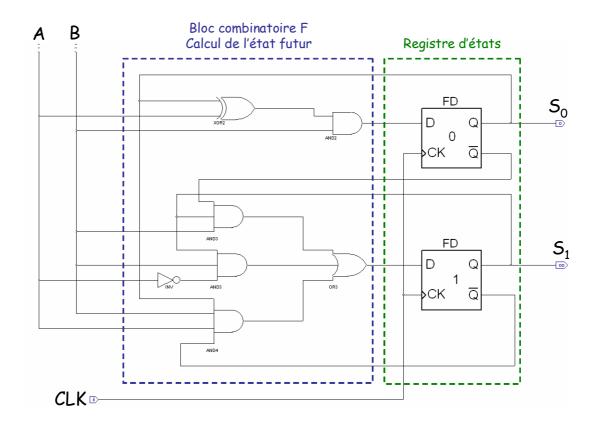

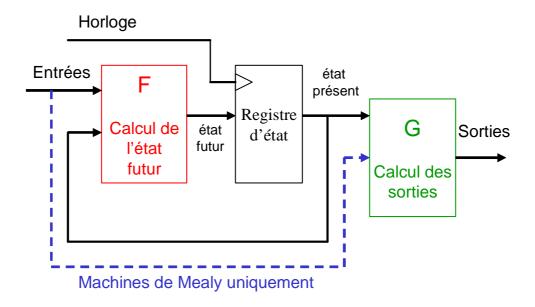

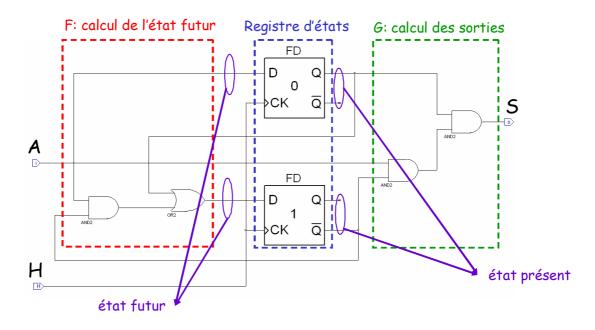

La figure 3 donne la structure générale d'un automate pouvant réaliser n'importe quelle fonction logique séquentielle synchrone. Nous reviendrons sur ce type d'architecture dans la suite du cours. Pour le moment, il suffit de savoir que le registre d'état est une assemblée de bascules passant d'un état à un autre, en fonction des entrées, à chaque impulsion du signal d'horloge.

Le registre constitue le coeur de l'automate. Ces sorties constituent l'état présent de l'automate. Les parties G et F sont des blocs combinatoires calculant, respectivement, les sorties et l'état futur de l'automate.

Etats futurs = F(état présent, entrées)

sorties = G(état présent) ou G(état présent, entrées)

figure 3 Structure générale des automates séquentiels

En pratique on distingue deux types d'architectures : les machines de Moore et les machines de Mealy. Dans les machines de Moore les sorties ne dépendent que de l'état présent. Au contraire dans les machines de Mealy les sorties dépendent à la fois de l'état présent et des entrées du système.

Avant de voir plus en détails la conception et la synthèse des automates câblés, il est indispensable de savoir analyser un circuit séquentiel, autrement dit d'être capable de comprendre le fonctionnement d'un circuit en étudiant son schéma. C'est l'objet du second chapitre.

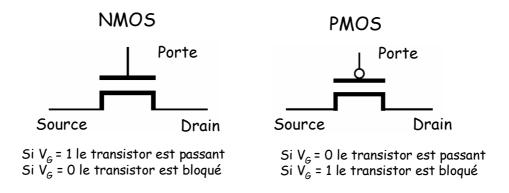

#### 1.4.2. Réalisation physique des automates.

Aujourd'hui, pour fabriquer un automate on n'utilise quasiment plus les circuits intégrés réalisés en technologie *SSI* ( Small Scale Integration, la fameuse série 7400). Cette technologie, très en voque dans les années 1970, présente de nombreux inconvénients :

Chaque composant ne comporte que quelques portes logiques.

Pour changer de fonction logique il faut changer de composant et refaire le circuit.

Une fois le circuit réalisé les connexions sont fixes.

Depuis une quinzaine d'années les fabricants proposent des circuits qui intègrent un grand nombre de portes logiques dont les interconnexions ne sont pas fixes. Ces composants sont donc reconfigurables à volonté par l'utilisateur. Les deux grandes familles actuelles sont :

Les circuits programmables par l'utilisateur. (PLD²)

Les circuits intégrés spécifiques (ASIC<sup>3</sup>)

De nombreux outils de conception assistée par ordinateur ont été développés pour utiliser ces composants. Ils libèrent le concepteur des taches les plus fastidieuses et lui permettent de se concentrer sur les points importants du processus de conception. Le chapitre 4 présente les principales caractéristiques de ces composants.

\_

<sup>&</sup>lt;sup>2</sup> Programmable Logic Device

<sup>&</sup>lt;sup>3</sup> Application Specific Integrated Circuit

# **Chapitre 2**

# Analyse des systèmes séquentiels.

#### 2.1. Modélisation des systèmes séquentiels asynchrones.

Autant il est relativement facile de trouver l'état stationnaire d'un système séquentiel, autant il est difficile de se représenter son évolution. Il est très utile de disposer d'un modèle. Nous commencerons par nous intéresser aux circuits asynchrones. Pour mémoire, il s'agit des circuits dont les entrées sont sensibles à des niveaux de tension (0 ou 1 par opposition aux transitions  $\uparrow$  ou  $\downarrow$ )

#### 2.1.1. Retour sur les systèmes combinatoires et séquentiels.

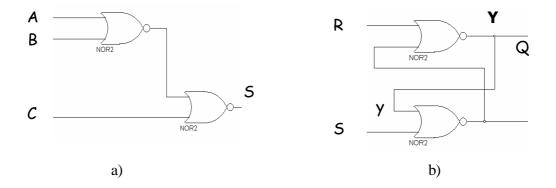

Dans un système combinatoire les différentes grandeurs logiques peuvent se calculer de proche en proche, en partant des entrées et en se dirigeant vers les sorties (voir la figure 4.a). A un instant donné, l'état du système est entièrement déterminé par les valeurs des entrées, mais aussi par les retards qu'introduisent les différents composants<sup>4</sup>. Une modification des entrées n'entraîne pas un changement instantané de la sortie!

Un circuit séquentiel est un circuit dans lequel les grandeurs logiques (y par exemple) ne peuvent pas toujours être calculées de proche en proche, du fait d'un certain nombre de bouclage qui ramènent la sortie vers l'entrée de un ou plusieurs circuits. Sur la figure 4.b La connaissance de y est indispensable au calcul de Q, mais y n'est pas déterminée uniquement par R et S: y est devenue une variable indépendante, on dira que c'est **une variable secondaire**. Le problème est que c'est une variable indépendante spéciale puisqu'elle influe sur sa propre valeur par l'intermédiaire de Q!

\_

<sup>&</sup>lt;sup>4</sup> Les retards sont liès au temps de propagation du signal à travers le circuits.

figure 4 a) exemple de circuit combinatoire. b) exemple de circuit séquentiel

#### 2.1.2. Un modèle de système séquentiel pour les circuits asynchrones.

Peut-on attribuer une valeur à une variable secondaire, telle que y, qui est elle même générée par le système? La réponse est oui, grâce précisément aux retards. Il existe un temps T pendant lequel la variable secondaire ne subit pas le contre-coup du bouclage (c'est à dire que le système n'a pas encore eu le temps d'agir sur elle), et constitue donc bien une variable indépendante.

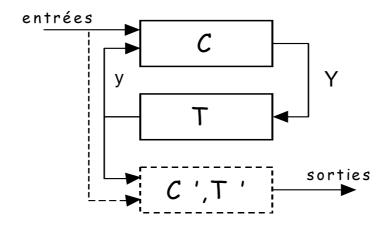

On peut modéliser un circuit séquentiel par le schéma représenté sur la figure 5. Les variables secondaires et les entrées commandent un ensemble combinatoire "instantané", c'est à dire supposé dépourvu de tout retard; c'est le bloc  $\mathcal{C}$  qui génère les excitations secondaires  $\mathcal{Y}$ . Ces dernières, après un certain retard symbolisé par le bloc  $\mathcal{T}$ , fournissent les nouvelles valeurs des variables secondaires  $\mathcal{Y}$  et ainsi de suite :

$$y(t) = Y(t-T)$$

Les excitations secondaires Y représentent les valeurs futures des variables secondaires y. En général, dans ce polycopié, on utilise plutôt les termes valeur future pour Y et valeur présente pour y.

Les sorties sont fabriquées directement à partir des variables secondaires et des entrées (circuit C' et retard T' sur la figure 5)

figure 5 Modélisation d'un système séquentiel

#### 2.1.3. Etat présent, état futur.

Le modèle précédent nous permet d'introduire les notions d'état présent et d'état futur. Quand nous parlerons de l'état d'un système il s'agira de l'état présent.

L'état présent est défini par la valeur des variables secondaires. La donnée de l'état présent et des entrées détermine entièrement le système, y compris sont évolution future. En particulier les sorties se calculent à partir de l'état présent et des entrées.

L'état futur est défini par la valeur des excitations secondaires. C'est à dire par les futures valeurs des variables secondaires. Rappelons que les excitations secondaires se calculent à partir des variables secondaires et des entrées en utilisant les expressions combinatoires des circuits *C*.

L'état futur devient le nouvel état présent au bout d'un temps de l'ordre du plus grand des retards T utilisés dans le modèle. Si l'on ne prend en compte que les retards induits par la propagation du signal, alors les limites sont imposées par la technologie.

Le système évolue jusqu'à ce que l'état présent et l'état futur soient identiques, on dit alors que le système est dans un **état stable**. A l'inverse, si le système ne trouve pas d'état stable, il oscille indéfiniment entre plusieurs états.

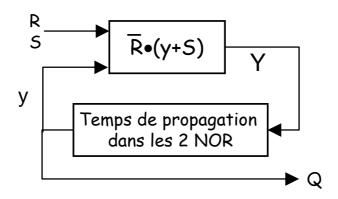

#### 2.1.4. Un exemple simple : la bascule RS.

Reprenons l'exemple de la bascule RS à base de portes NOR. Choisissons comme variable secondaire la deuxième entrée de la porte S, c'est à dire aussi la sortie Q (voir la figure 6). L'excitation secondaire Y est égale à , et y et Q deviennent égales à Y au bout d'un temps égal au temps de propagation du signal à travers les deux portes NOR. On note souvent l'excitation secondaire Y directement sur le schéma électronique (ici à la place de Q) pour symboliser l'état futur ; mais attention, il ne faut pas perdre de vue que Q et y sont des

grandeurs réelles alors que Y n'existe que dans notre modèle de représentation des systèmes séquentiels

figure 6 Modélisation d'une bascule RS

Ecrivons les états présents et futurs pour les diverses combinaisons des entrées.

$$S = 1, R = 0 \text{ impose } Y = 1 \text{ donc}: \begin{cases} \text{pr\'esent } y = 0 \Rightarrow \text{futur } Y = 1 \\ \text{pr\'esent } y = 1 \Rightarrow \text{futur } Y = 1 \end{cases} \quad \text{l'\'etat } y = 1 \text{ est stable.}$$

$$S = 0, R = 1 \text{ impose } Y = 0 \text{ donc}: \begin{cases} \text{pr\'esent } y = 0 \Rightarrow \text{futur } Y = 0 \\ \text{pr\'esent } y = 1 \Rightarrow \text{futur } Y = 0 \end{cases} \quad \text{l'\'etat } y = 0 \text{ est stable.}$$

$$S = 0, R = 0 \text{ impose } Y = y \text{ donc}: \begin{cases} \text{pr\'esent } y = 0 \Rightarrow \text{futur } Y = 0 \\ \text{pr\'esent } y = 1 \Rightarrow \text{futur } Y = 1 \end{cases} \quad \text{les \'etats } y = 1 \text{ et } y = 0$$

sont stables.

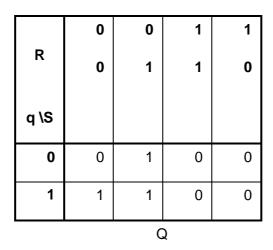

Les résultats précédents peuvent être regroupés en une seule table donnant la valeur de l'excitation secondaire Y en fonction des variables R, S et y, et que l'on appelle table des excitations secondaires

|   | R | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|

| у | S | 0 | 1 | 1 | 0 |

| 0 |   | 0 | 1 | 0 | 0 |

| 1 |   | 1 | 1 | 0 | 0 |

|   |   |   |   |   |   |

Précisons que la disposition des entrées en combinaisons adjacentes n'est pas

obligatoire, mais simplement commode.

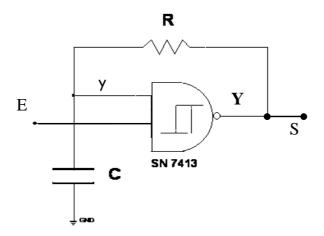

#### 2.1.5. Deuxième exemple: l'astable.

Considérons maintenant le montage de la figure 7. La variable secondaire y est la seconde entrée de la porte NAND et l'excitation secondaire la sortie de cette même porte. Contrairement à l'exemple précédent, le retard T n'est plus fixé par le temps de propagation du signal à travers la porte logique, mais par le circuit RC intégré dans la boucle de retour. La sortie est S=y

L'excitation secondaire s'écrit  $Y=\overline{E\bullet y}=\overline{E}+\overline{y}$ . On a donc les deux situations suivantes :

$$E = 0 \Rightarrow Y = 1$$

, l'état  $y = 1$  est donc stable.

$$E = 1 \Rightarrow Y = y$$

par conséquent  $\begin{cases} si \text{ l'état présent est y = 1 alors l'état futur est Y = 0} \\ si \text{ l'état présent est y = 0 alors l'état futur est Y = 1} \end{cases}$

Ce qui donne la table des transitions suivante :

| Е | 0 | 1 |

|---|---|---|

| y |   |   |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

|   | Y |   |

Pour E=1 il n'y a pas d'état stable, le circuit oscille entre les deux états y=0 et y=1 avec une périodicité de l'ordre de T déterminée par le circuit RC. On peut utiliser ce type de circuit pour réaliser une horloge commandable (E=0 l'horloge est bloquée, E=1 l'horloge fonctionne)

figure 7 Circuit astable

#### 2.1.6. Conclusion pour les circuits asynchrones.

Il y a au moins trois points importants à retenir des deux exemples précédents.

- La correspondance état présent ⇒ état futur est spécifique de chaque combinaison des entrées. En particulier un état stable pour certaines valeurs des entrées est instable pour d'autres

- 2. Il peut arriver que pour certaines entrées il n'existe aucun état stable. Le système asynchrone oscille alors librement entre plusieurs états à une fréquence caractéristique des constantes du système.

- 3. Les constantes de temps d'un système asynchrone sont souvent imposées par les temps de retard introduit par les circuits logiques mais pas uniquement. Le concepteur peut introduire volontairement des retards artificiels supplémentaires comme dans le cas de l'astable.

### 2.2. Modélisation des systèmes synchrones.

#### 2.2.1. Systèmes synchrones avec horloge.

Ce sont des systèmes particuliers répondant aux caractéristiques suivantes :

- Ils possèdent une entrée particulière, baptisée horloge, alimentée par des impulsions.

- Les signaux sur les autres entrées sont des niveaux 0 ou 1.

A chaque impulsion d'horloge il se produit au plus un changement d'état (l'état futur devient de l'état présent).

En général les circuits synchrones avec horloge sont simplement appelés circuits ou

systèmes synchrones. Ils sont de plus en plus répandus. En effet, dans de nombreux systèmes complexes, les ordinateurs par exemple, les opérations doivent être parfaitement cadencées de manière à se produire dans un ordre bien déterminé. La synchronisation par une horloge commune est alors indispensable.

Les systèmes synchrones complexes sont construits à partir des circuits élémentaires que sont les bascules synchrones ( *JK*, *D*, *RS*).

#### 2.2.2. Evolution temporelle des systèmes synchrones.

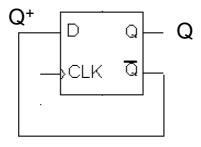

Dans les systèmes synchrones la présence de l'horloge introduit une temporisation "infinie" entre l'état présent et l'état futur, ce qui simplifie beaucoup la modélisation. En particulier,

L'état présent est défini par les valeurs des sorties  $Q_i$  des bascules. Par contre, l'état futur est entièrement déterminé par les valeurs des entrées des bascules avant l'impulsion d'horloge. Dans la plus part des ouvrages on note  $Q_i^+$  les valeurs futures des sorties des bascules :  $Q_i^+ = f$  (entrées des bascules)

On peut se dispenser de la modélisation en variables secondaires et excitations secondaires. On écrit directement les valeurs des entrées dans l'état présent et on en déduit les futures valeurs des sorties.

Le système n'évoluant pas entre deux impulsions d'horloge, il n'y a plus de notion d'état stable ou, ce qui revient au même, tous les états sont stables!

A la différence des systèmes asynchrones, l'état présent et l'état futur sont physiquement accessibles sur le circuit.

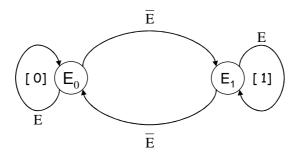

Considérons, par exemple, le circuit représenté sur la figure 2.5. L'état présent est défini par la valeur Q de la sortie de la bascule. Puisqu'il s'agit d'une bascule D la valeur de l'entrée à l'instant t constitue la valeur future de la sortie  $D=Q^+$ . Comme par ailleurs,  $D=\overline{Q}$  on a  $Q^+=\overline{Q}$  et on comprend immédiatement que la sortie Q va commuter à chaque impulsion d'horloge (fonctionnement en bascule T).

figure 8 Exemple de système séquentiel

#### 2.3. Analyse fonctionnelle des systèmes séquentiels.

Le problème est le suivant : comment comprendre et analyser le fonctionnement d'un circuit dont on ne connaît que le schéma de câblage? La réponse est assez simple si on utilise le modèle précédent de représentation des circuits séquentiels et que l'on procède par étapes.

#### 2.3.1. Les différentes étapes.

1<sup>ere</sup> étape : repérage des boucles de retour et identification des variables secondaires.

Sur le schéma on repère les différentes boucles de retour ainsi que les blocs séquentiels (par exemple des bascules). On affecte à chaque boucle et à chaque bloc séquentiel une variable secondaire (et donc une excitation secondaire).

2<sup>eme</sup> étape : écriture de la table des transitions ( ou des excitations secondaires).

A partir du schéma du circuit, on déduit les expressions logiques combinatoires permettant de calculer les valeurs futures  $\mathcal{Q}_i^+$  en fonction des valeurs présentes  $\mathcal{Q}_i^-$  s'il s'agit d'un circuit asynchrone, les excitations secondaires  $X_i^-$  en fonction des variables secondaires  $x_i^-$ . On remplit ensuite une table donnant les valeurs futures pour toutes les combinaisons possibles des valeurs présentes et des entrées : c'est la table des transitions (ou des excitations secondaires). Comme nous avons déjà commencé à le voir, c'est un tableau à double entrée ; les différentes combinaisons des variables secondaires sont écrites verticalement, et celles des entrées horizontalement. Une remarque néanmoins sur la présentation de ces tables. Dans le cas des systèmes synchrones avec horloge, on ne représente pas l'entrée d'horloge. Il est toujours implicite que le passage d'un état à un autre, se produit au moment de l'impulsion d'horloge.

Pour fixer les idées considérons un système à deux entrées A et B, et deux variables secondaires x et y, les tables des excitations secondaires se présentent donc de la façon suivante :

| Α            | 0   | 0   | 1   | 1   |

|--------------|-----|-----|-----|-----|

| <i>x y</i> B | 0   | 1   | 1   | 0   |

| 0 0          | 0 0 | 0 1 | 0 1 | 0 1 |

| 0 1          | 1 1 | 0 1 | 0 0 | 1 1 |

| 1 1          | 1 1 | 1 0 | 1 0 | 1 0 |

| 1 0          | 0 0 | 1 0 | 1 1 | 0 0 |

X, Y

3<sup>eme</sup> étape : construction de la table des états et de la table des sorties.

Pour construire la table des états on donne un nom (il s'agit souvent d'un numéro ou d'une lettre) à chaque état présent  $(x \ y)$  et on réécrit la tables des transitions avec ce codage. Décidons, par exemple, du codage suivant :

xy = 00 est l'état E1

xy = 0.1 est l'état E2

xy = 11 est l'état E3

xy = 10 est l'état E4

La table des états est alors :

| Α         | 0  | 0  | 1  | 1  |

|-----------|----|----|----|----|

| présent B | 0  | 1  | 1  | 0  |

| E1        | E1 | E2 | E2 | E2 |

| E2        | E3 | E2 | E1 | E3 |

| E3        | E3 | E4 | E4 | E4 |

| E4        | E1 | E4 | E3 | E1 |

futur

Les tables des états sont un peu redondantes avec celles des transitions et apportent peu d'informations supplémentaires lors de l'analyse d'un circuit. Nous verrons plus loin dans ce cours quelles sont beaucoup plus utiles lors de la synthèse d'un système séquentiel.

La, ou les sorties, du système dépendent des valeurs présentes  $Q_i$  (ou des variables secondaires x, y....) et éventuellement des entrées A, B ... Pour dresser la table des sorties on établi à partir du schéma les expressions logiques combinatoires donnant la valeur des différentes sorties. On reporte ensuite dans une table les valeurs des sorties pour chaque état et, éventuellement, pour chaque combinaison des entrées.

4<sup>eme</sup> étape : représentation du diagramme d'états et identification de la finalité du circuit.

Un diagramme d'états visualise les changements d'états du système et permet d'en comprendre le fonctionnement. Nous en avons vu un exemple dans l'introduction lorsque nous avons décrit le fonctionnement d'un monte-charge.

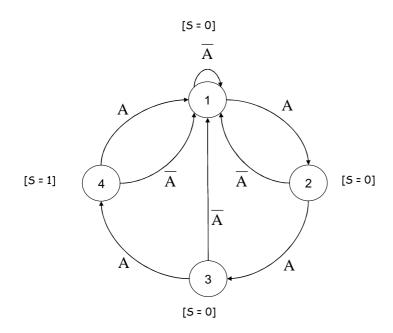

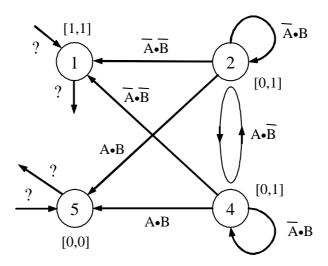

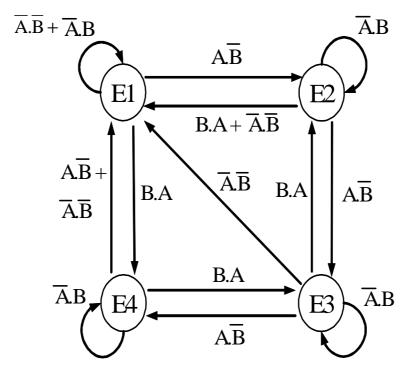

Dans ce diagramme chaque état est représenté par un rond qui porte son nom (ou son numéro). A partir de chaque rond des flèches indiquent les transitions possibles, chacune d'entre elles étant associée à une combinaison des entrées. Là encore, pour un système synchrone pulsé, les combinaisons des entrées sont remplacées par la désignation de l'entrée active. Les flèches bouclées sur elles mêmes indiquent, s'il-y-a lieu, les oscillations. Enfin, on peut également y inscrire la valeur des sorties dans les différents états. Le diagramme correspondant aux tables précédentes est donné sur la figure 9.

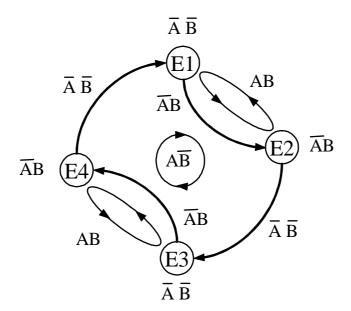

figure 9 Diagramme d'états correspondant aux tables précédentes. Pour les synchrones avec horloge les transitions se produisent au moment des impulsions d'horloge

Nous allons appliquer cette méthode d'analyse sur des exemples concrets de systèmes asynchrones ou synchrones avec horloge.

#### 2.3.2. Analyse d'un système asynchrone.

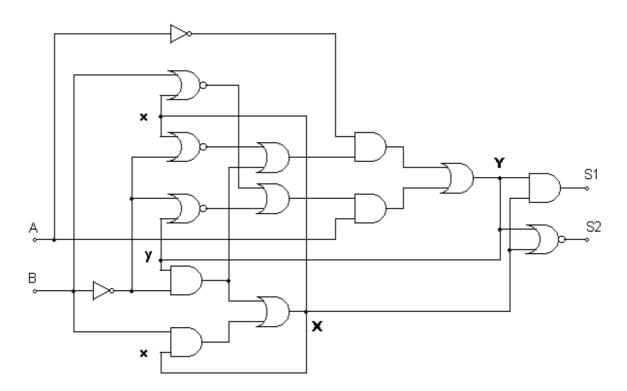

Etudions le système asynchrone représenté sur la figure 10. Le circuit comporte deux boucles de retour et aucun bloc séquentiel non détaillé. Deux variables secondaires, x et y, sont placées sur le schéma ainsi que les deux excitations secondaires correspondantes X et Y.

**1.** A partir du schéma on établi les expressions combinatoires permettant de calculer les excitations secondaires *X* et *Y*.

$$X = \overline{B} \bullet y + B \bullet x$$

$$Y = \overline{A} \bullet (B \bullet \overline{x} + \overline{B} \bullet y) + A \bullet (\overline{B} \bullet \overline{x} + B \bullet \overline{y})$$

On remplit ensuite la table des excitations secondaires :

| Α                   | 0   | 0   | 1   | 1   |

|---------------------|-----|-----|-----|-----|

| <i>x y</i> <b>B</b> | 0   | 1   | 1   | 0   |

| 0 0                 | 0 0 | 0 1 | 0 1 | 0 1 |

| 0 1 | 1 1                 | 0 1 | 0 0 | 1 1 |

|-----|---------------------|-----|-----|-----|

| 1 1 | 1 1                 | 1 0 | 1 0 | 1 0 |

| 1 0 | 0 0                 | 1 0 | 1 1 | 0 0 |

|     | <i>X</i> , <i>Y</i> |     |     |     |

figure 10 : Exemple de circuit asynchrone. Les deux variables secondaires x et y sont indiquées sur le schéma ainsi que les excitations secondaires correspondantes

2. La table des excitations secondaires est identique à celle que nous avons écrite dans le paragraphe 2.3. En reprenant le même codage pour les états on obtient immédiatement la table des états.

| le        | codage      |  |

|-----------|-------------|--|

| xy = 0 0  | ⇒ l'état E1 |  |

| x y = 0 1 | ⇒ l'état E2 |  |

| x y = 1 1 | ⇒ l'état E3 |  |

| x y = 10  | ⇒ l'état E4 |  |

| А         | 0  | 0  | 1  | 1  |

|-----------|----|----|----|----|

| présent B | 0  | 1  | 1  | 0  |

| E1        | E1 | E2 | E2 | E2 |

| E2        | E3 | E2 | E1 | E3 |

| E3        | E3 | E4 | E4 | E4 |

| E4        | E1 | E4 | E3 | E1 |

futur

donne

A partir de la table des états, on remarque que les états E1 et E3 sont stables lorsque AB = 00. De la même façon les états E2 et E4 sont stables pour AB = 01. A l'inverse il n'existe aucun état stable pour les entrées AB = 11 et AB = 10.

Les sorties dépendent des entrées A et B et de l'état présent x y. A partir du schéma on établi les expressions combinatoires :

$$S_{1} = (\overline{B} \bullet y + B \bullet x) \bullet (\overline{A} \bullet (B \bullet \overline{x} + \overline{B} \bullet y) + A \bullet (\overline{B} \bullet \overline{x} + B \bullet \overline{y}))$$

$$S_{2} = (\overline{B} \bullet y + B \bullet x) + (\overline{A} \bullet (B \bullet \overline{x} + \overline{B} \bullet y) + A \bullet (\overline{B} \bullet \overline{x} + B \bullet \overline{y}))$$

que l'on peut réécrire avec beaucoup de prudence sous la forme :

$$S_1 = X \bullet Y$$

$$S_2 = \overline{X + Y}$$

en se souvenant que les excitations secondaires n'ont aucune existence réelle. On remplie aisément la table des sorties.

| Α                   | 0   | 0   | 1   | 1   |

|---------------------|-----|-----|-----|-----|

| <i>x y</i> <b>B</b> | 0   | 1   | 1   | 0   |

| 0 0                 | 0 1 | 0 0 | 0 0 | 0 0 |

| 0 1                 | 1 0 | 0 0 | 0 1 | 1 0 |

| 1 1                 | 1 0 | 0 0 | 0 0 | 0 0 |

| 1 0                 | 0 1 | 0 0 | 1 0 | 0 1 |

| $S_1, S_2$          |     |     |     |     |

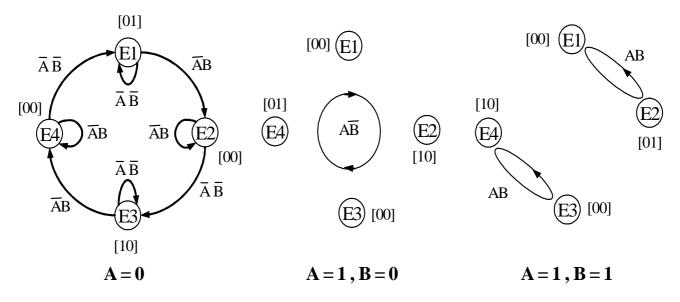

**3.** Le diagramme d'états à déjà été présenté à la fin du paragraphe 2.3.1 Nous le redessinons sur la figure 11 en y ajoutant les valeurs des sorties  $S_1$   $S_2$  et en séparant les différents modes de fonctionnement. A gauche est représenté le "régime stable" (A = 0) dans lequel les sorties oscillent entre 0 et 1 en opposition de phase en fonction des cycles  $0 \rightarrow 1 \rightarrow 0$  sur l'entrée B. Au centre on trouve l'oscillation "automatique" sur les 4 états lorsque AB = 10. Les sorties évoluent toujours en opposition de phase. Enfin, à droite est représentée l'oscillation du système sur 2 états lorsque AB = 11. Selon les conditions initiales, c'est à dire selon l'état de départ, une sortie reste à 0 pendant que l'autre oscille

entre 0 et 1.

figure 11 Les 3 modes de fonctionnement du circuit asynchrone de la figure 10

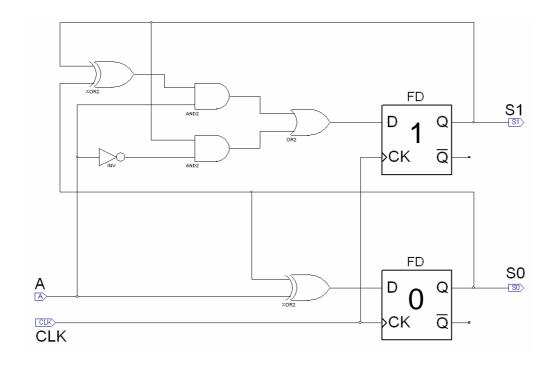

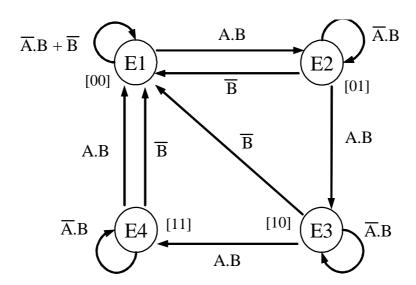

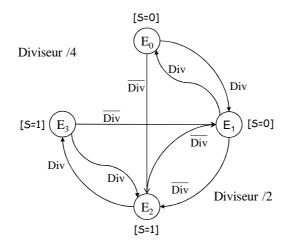

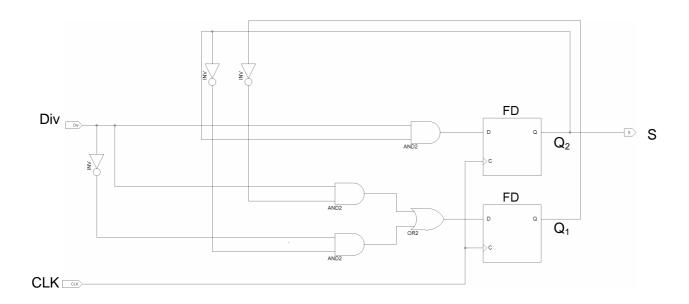

# 2.3.3. Analyse d'un système synchrone (1er exemple).

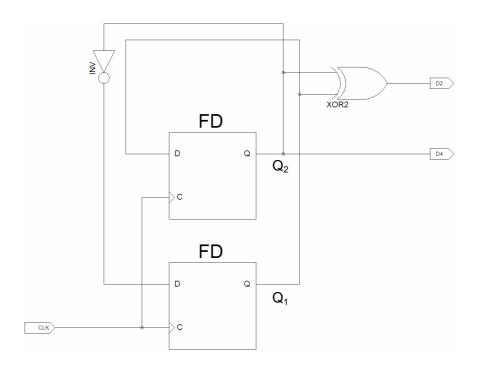

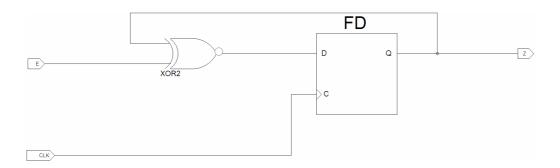

Nous allons analyser le fonctionnement du circuit représenté sur la figure 12. La démarche est similaire à celle utilisée pour un système asynchrone. L'état présent est maintenant défini par les valeurs des sorties  $Q_1$   $Q_0$  des deux bascules, alors que l'état futur  $Q_1^+$   $Q_0^+$  est entièrement déterminé par les valeurs des entrées des bascules avant l'impulsion d'horloge  $Q_i^+ = f$  (entrées des bascules). Les entrées  $D_0$  et  $D_1$  sont gouvernées par les expressions :

$$D_1 = A \bullet (Q_0 \oplus Q_1) + \overline{A} \bullet Q_1$$

$$D_0 = Q_0 \oplus A$$

figure 12

Pour obtenir les valeurs futures  $\mathcal{Q}_i^+$  il faut se souvenir qu'une bascule D recopie sur sa sortie la valeur présente sur son entrée au moment de l'impulsion d'horloge.  $\mathcal{Q}_i^+(t) = D_i(t-1)$ . On obtient ainsi la table des transitions :

| $Q_1 \ Q_0$ | 1   | 0   |

|-------------|-----|-----|

| 0 0         | 0 1 | 0 0 |

| 0 1         | 1 0 | 0 1 |

| 1 1         | 0 0 | 1 1 |

| 1 0         | 1 1 | 1 0 |

$$Q \stackrel{+}{_1} Q \stackrel{+}{_0}$$

On code ensuite les états et on en déduit la table des états<sup>5</sup>:

| le codage                                     |       | A<br>présent | 1  | 0  |

|-----------------------------------------------|-------|--------------|----|----|

| $Q_1 Q_0 = 0 0 \Rightarrow \text{ \'etat E1}$ |       | E1           | E2 | E1 |

| $Q_1 Q_0 = 0.1 \Rightarrow \text{état E2}$    | donne | E2           | E3 | E2 |

| $Q_1 Q_0 = 1 0 \implies \text{état E3}$       | domio | E3           | E4 | E3 |

| $Q_1 Q_0 = 1.1 \implies \text{\'etat E4}$     |       | E4           | E1 | E4 |

|                                               |       |              |    |    |

état futur

Il faut bien comprendre que l'horloge est toujours présente, même si elle ne figure explicitement dans aucune de ces tables. Les changements d'états ne se produisent qu'au moment des impulsions d'horloge.

Dans cet exemple, les sorties du circuit ne dépendent que de l'état présent  $\mathcal{Q}_1\,\mathcal{Q}_0$  et jamais de l'entrée A. Elles s'expriment :

$$S_1 = Q_1$$

$$S_0 = Q_0$$

puisqu'elles correspondent directement aux sorties des bascules ! La table des sorties est ainsi

| état | S <sub>1</sub> S <sub>0</sub> |

|------|-------------------------------|

| E1   | 0 0                           |

| E2   | 0 1                           |

| E3   | 1 0                           |

| E4   | 1 1                           |

<sup>&</sup>lt;sup>5</sup> Rien n'oblige à utiliser un codage identique à celui de l'exemple précédent.

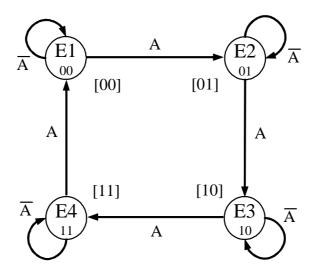

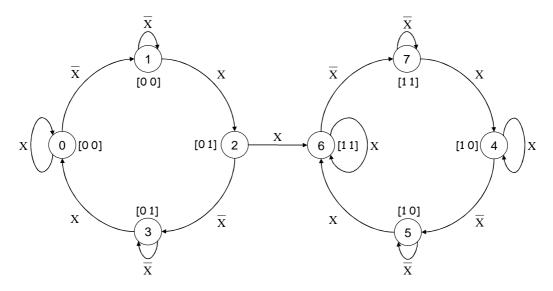

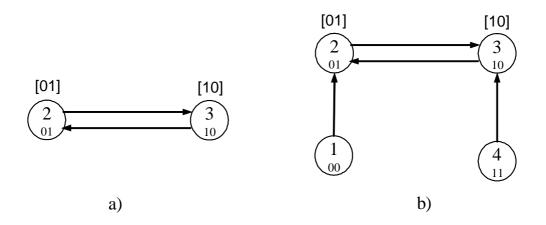

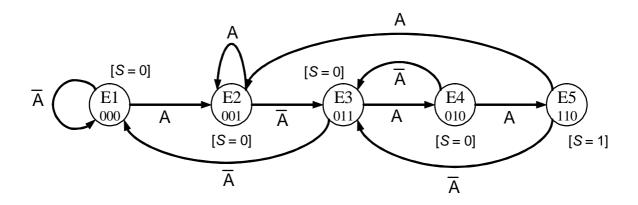

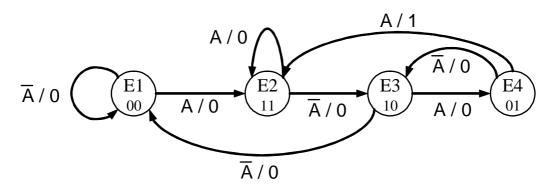

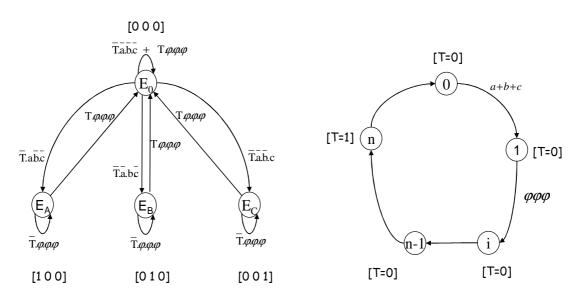

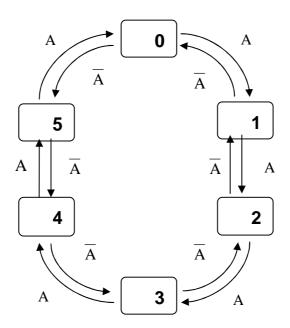

figure 13 Diagramme des transitions. Pour chaque état le codage  $Q_1Q_0$  est indiqué. Les sorties  $\left[S_1S_0\right]$  associées à chaque état sont également reportées

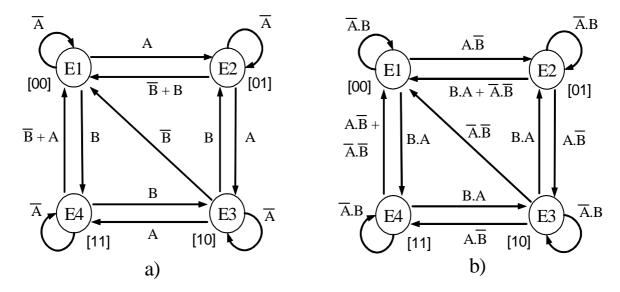

Le diagramme d'états illustrant le fonctionnement de ce système est donné sur la figure 13. Quel que soit l'état de départ et la valeur de l'entrée A, il y a toujours une transition active ; le système change ainsi d'état à chaque front montant du signal d'horloge. A partir de l'état E1  $(Q_1Q_0=00)$  l'évolution du système, **au fur et à mesure des impulsions d'horloge**, est la suivante :

- Si A = 1 l'automate décrit un cycle en passant successivement dans les états E1, E2, E3 et E4.

- Si A = 0 l'automate reste dans l'état ou il se trouve.

La fonction réalisée par ce montage est obtenue en analysant l'évolution des sorties. Lorsque A = 1 les sorties  $S_1S_0$  prennent successivement les valeurs 00, 01, 10, 11, 00 ... Il s'agit donc d'un compteur par 4 actif lorsque A = 1. L'entrée A = 0 bloque le compteur dans son état présent.

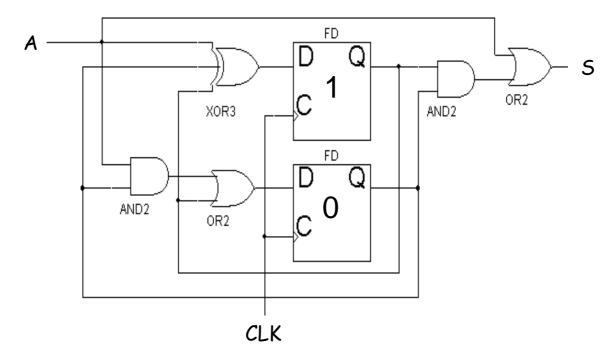

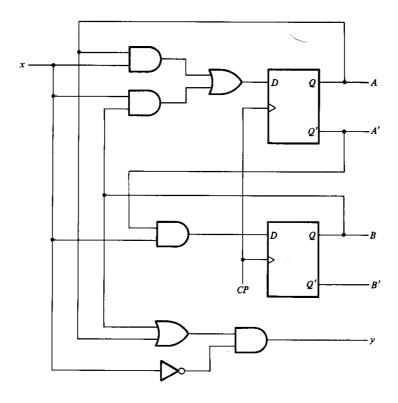

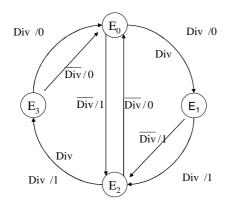

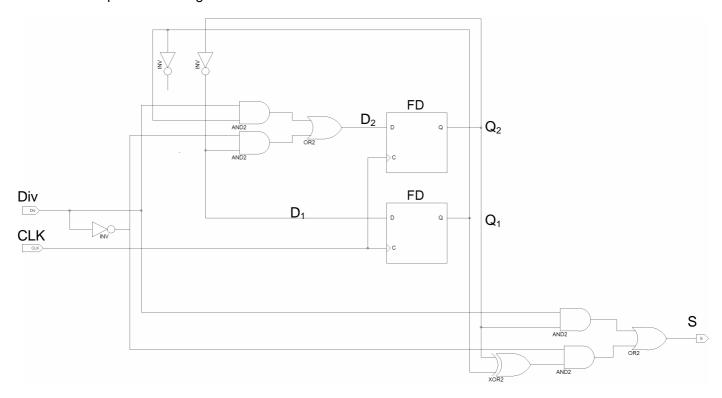

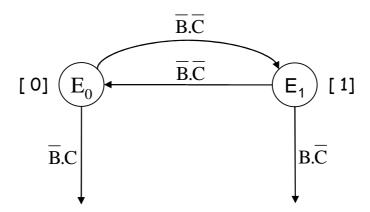

#### 2.3.4. Analyse d'un système synchrone (2<sup>eme</sup> exemple).

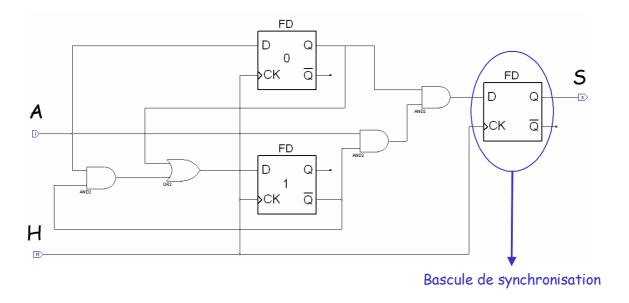

Analysons maintenant le circuit représenté sur la figure 14. Le circuit ressemble beaucoup à celui que nous avons analysé précédemment. Il y a pourtant une différence importante ; elle concerne la sortie qui maintenant dépend explicitement de l'entrée A. Nous verrons que cela affecte significativement le fonctionnement du circuit et nous oblige a présenter un peu différemment le diagramme d'états.

Pour le moment procédons comme dans le paragraphe 2.3.3 pour analyser le circuit. Les équations de commande des deux bascules D s'écrivent :

$$D_1 = A \oplus Q_0 \oplus Q_1$$

$$D_0 = A \bullet Q_0 + Q_1$$

On obtient ainsi la table des transitions :

| Q <sub>1</sub> Q <sub>0</sub> | 1   | 0   |

|-------------------------------|-----|-----|

| 0 0                           | 1 0 | 0 0 |

| 0 1                           | 0 1 | 1 0 |

| 1 1                           | 1 1 | 0 1 |

| 1 0                           | 0 1 | 1 1 |

$$Q_1^+ Q_0^+$$

$$D_{1} D_{0}$$

On code ensuite les états et on en déduit la table des états:

le codage

$$Q_1 Q_0 = 0.0 \Rightarrow \text{ état E1}$$

$$Q_1 Q_0 = 0.1 \Rightarrow \text{ \'etat E2}$$

$Q_1 Q_0 = 1.1 \implies \text{état E3}$

$$Q_1 Q_0 = 10 \implies \text{état E4}$$

| A<br>présent | 1  | 0  |

|--------------|----|----|

| E1           | E4 | E1 |

| E2           | E2 | E4 |

| E3           | E3 | E2 |

| E4           | E2 | E3 |

état futur

Une fois encore l'horloge est explicitement présente dans ces deux tables et les changements d'états ne se produisent qu'au moment des impulsions d'horloge.

donne

figure 14

La sortie S dépend à la fois de l'état présent  $\mathcal{Q}_1\,\mathcal{Q}_0$  et de l'entrée  $\mathbf{A}$ . Elle s'exprime:

$$S = A + Q_0 \bullet Q_1$$

On en déduit la table des sorties dans laquelle figure maintenant l'entrée A

| Α<br>Q <sub>1</sub> Q <sub>0</sub> | 1 | 0 |

|------------------------------------|---|---|

| 0 0                                | 1 | 0 |

| 0 1                                | 1 | 0 |

| 1 1                                | 1 | 1 |

| 1 0                                | 1 | 0 |

|                                    | C |   |

A la différence du circuit synchrone étudié dans le paragraphe 2.3.3, on ne peut plus associer une valeur de la sortie à chaque état! Pour un même état la valeur de la sortie dépend de l'entrée A. Ainsi, pour l'état E1 ( $Q_1$   $Q_0$  = 00) on a S = 1 si A = 1 et S = 0 si A = 0.

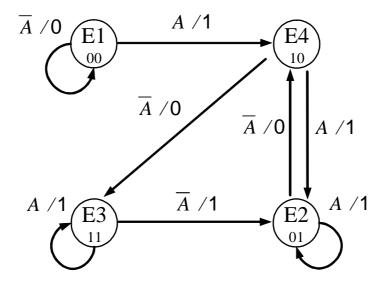

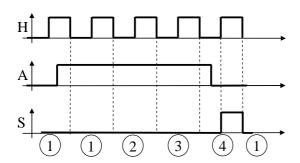

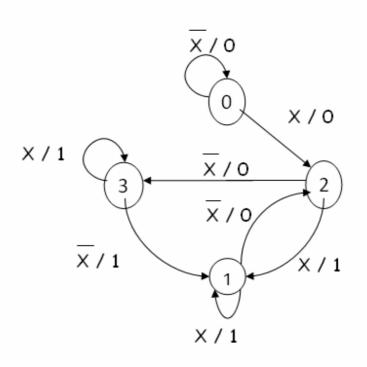

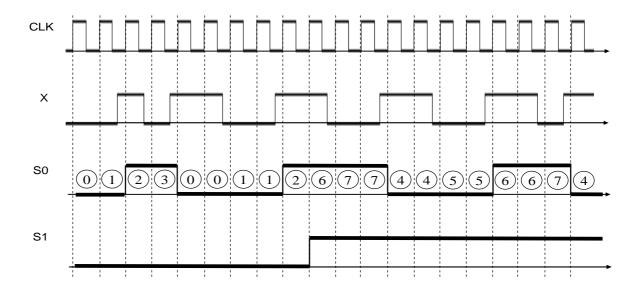

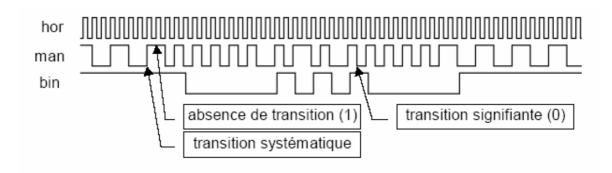

Le diagramme d'états associé à ce circuit est représenté sur la figure 15. Comme dans les exemples précédents, les flèches indiquent les transitions entre les états lorsque la condition sur l'entrée A est vérifiée au moment de l'impulsion d'horloge.

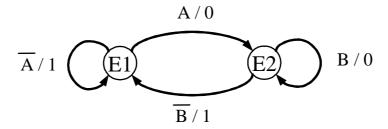

figure 15 Diagramme d'états du circuit représenté sur la figure 14

Pour tenir compte de l'action immédiate de l'entrée sur la sortie, on fait figurer la valeur de la sortie à coté de la condition de transition. Le diagramme de la figure 15 se lit donc de la façon suivante pour l'état E:

- Tant que A = 0 le système reste dans l'état E1 et la sortie S = 0.

- Dés que A = 1 la sortie devient S = 1 mais le système reste dans l'état E1 (pas d'impulsion d'horloge donc pas de transition)

- Si au moment de l'impulsion d'horloge on a toujours A = 1 alors le système évolue vers l'état E2 et la sortie reste S = 1 (elle repassera à 0 dés que A reviendra à 0).

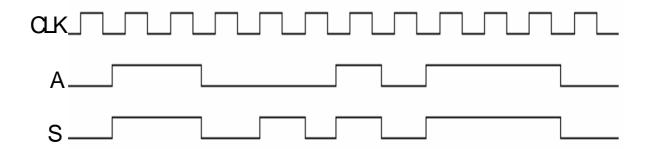

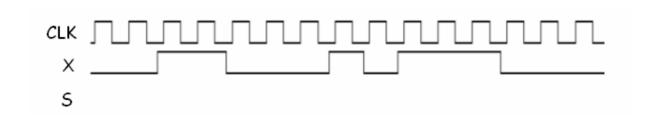

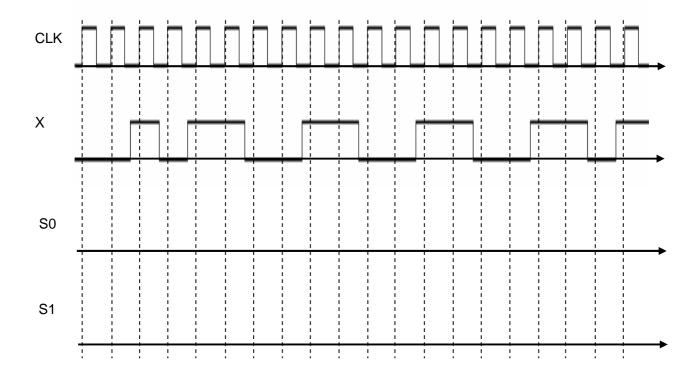

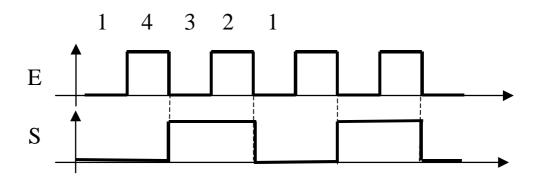

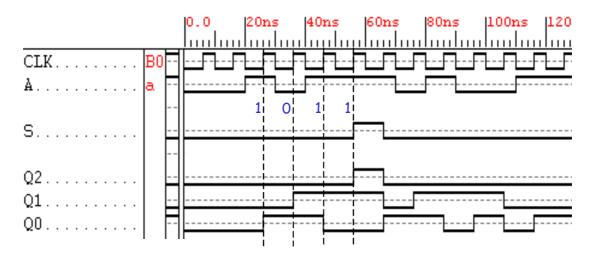

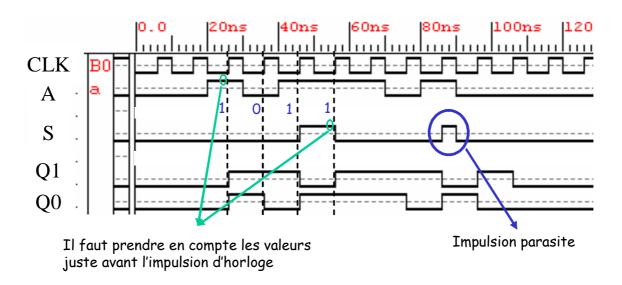

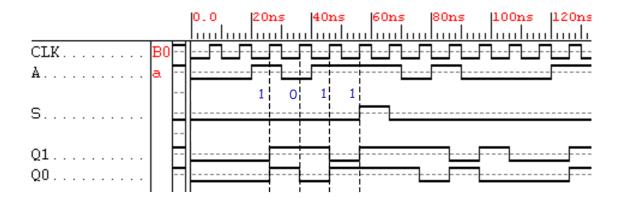

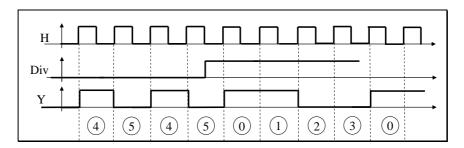

Sur le chronogramme de la figure qui illustre le fonctionnement de ce circuit, on observe bien .

#### 2.3.5. Comparaison des deux circuits synchrones analysés.

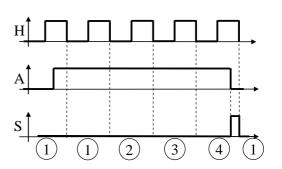

Les deux systèmes synchrones que nous venons d'analyser sont de nature différente. Celui du paragraphe 2.3.3 dans lequel la sortie ne dépend que de l'état présent (c'est-à-dire uniquement des sorties des bascules) est une machine de Moore. Sa sortie est toujours synchrone avec les impulsions de l'horloge.

A l'inverse, le circuit du paragraphe 2.3.4 est une machine de Mealy. Sa sortie dépend de l'état présent et de l'entrée. Elle n'est donc plus automatiquement synchrone avec les impulsions de l'horloge. Ce comportement est illustré sur le chronogramme de la figure 16 sur lequel on constate que la sortie S peut être synchrone avec l'entrée A et changer entre deux impulsions d'horloge. Nous reviendrons plus en détail sur ces deux types de machines dans le paragraphe 3.3

figure 16 Chronogramme illustrant le fonctionnement du circuit de la figure 14

#### 2.4. Intérêt des circuits synchrones avec horloge.

En pratique on utilise rarement des circuits séquentiels asynchrones. La principale raison du manque de fiabilité des systèmes asynchrones est liée à la notion de course critique.

#### 2.4.1. Notion de course critique : aléas.

La course critique est l'équivalent pour les systèmes séquentiels de l'aléa logique pour les systèmes combinatoires. Les courses critiques n'apparaissent que dans les systèmes asynchrones.

Considérons la table des excitations secondaires ci-dessous, et plaçons nous dans l'état  $y_1$   $y_2$  =01 stable sous l'entrée A = 0 (2 $^{\rm eme}$  ligne). Si A passe à la valeur 1 l'état présent va devenir  $y_1$   $y_2$  =1 0. Les deux variables secondaires  $y_1$  et  $y_2$  doivent donc changer de valeur "simultanément".

En réalité, une des variables va obligatoirement commuter un très court laps de temps avant l'autre et ceci peut gravement perturber le fonctionnement d'un système asynchrone. Ainsi, si la transition  $y_1$   $y_2 = 0.0$   $y_1$   $y_2 = 1.0$  passe par l'état intermédiaire  $y_1$   $y_2 = 0.0$  l'état final sera bien  $y_1$   $y_2 = 1.0$  qui est stable pour A=1. A l'inverse, si l'état intermédiaire est  $y_1$   $y_2 = 1.1$  (3<sup>eme</sup> ligne), le système se retrouve piégé dans cet état qui n'évolue pas quelque soit la valeur de l'entrée A. L'évolution finale de l'état  $y_1$   $y_2 = 0.1$  est donc aléatoire et dépend de la rapidité des circuits. Dans cet exemple le phénomène est ici d'autant plus grave que l'état  $y_1$   $y_2 = 1.1$  est un "piège" dans lequel le système restera bloqué quelle que soit la valeur de l'entrée. En pratique, dès que le circuit est un peu compliqué, il est impossible de connaître la variable secondaire qui va changer en premier ; tout dépend des retards introduits par les circuits et de la façon dont est câblé l'ensemble du montage.

La course  $A = 0 \rightarrow A=1$  est dite critique. Avant la généralisation des circuits synchrones, le remède consistait à éviter les changements non adjacents des variables secondaires par

un choix judicieux du codage des états. Aujourd'hui le remède consiste à ne jamais utiliser de circuits séquentiels asynchrones, et à toujours concevoir des systèmes à base de circuits synchrones avec horloge.

#### 2.4.2. Le rôle de l'horloge.

Dans une réalisation synchrone le rôle de l'horloge est de supprimer toute possibilité d'aléas dans l'évolution de l'état. Idéalement entre deux transitions actives de l'horloge le système est figé, son état ne peut pas changer. Dans la réalité le temps qui sépare deux front consécutifs du signal d'horloge est mis à profit pour que les circuits combinatoires puissent effectuer leurs calculs sans que leurs temps de retard (toujours non nuls) ne risque de provoquer d'ambiguïté dans la valeur de l'état futur.

#### 2.5. Analyse temporelle des systèmes séquentiels.

Dans les paragraphes précédents nous avons vu comment analyser un circuit pour en comprendre le fonctionnement (analyse fonctionnelle). Pour le moment, nous n'avons absolument pas tenu compte des contraintes, notamment temporelles, qu'impose la technologie sur le fonctionnement d'un circuit.

#### 2.5.1. Contraintes temporelles sur les bascules synchrones.

Pour fonctionner de façon nominale les circuits séquentiels, en particulier les bascules, doivent respecter un certain nombre de contraintes concernant la stabilité de leurs entrées avant et après l'impulsion d'horloge ou encore la fréquence maximum de l'horloge.

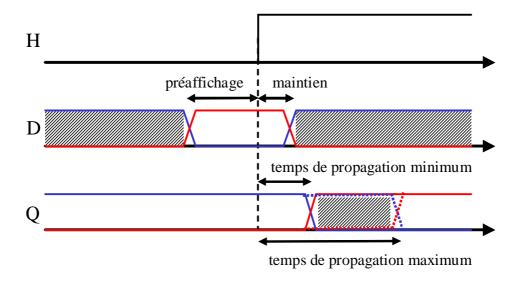

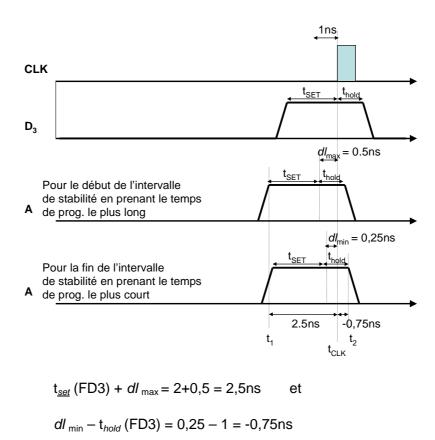

figure 17 Les temps caractéristiques de variation des entrées et sorties d'une bascule D synchrone

#### Les contraintes.

Considérons une bascule D synchrone. Son fonctionnement est bien connu : à chaque

impulsion d'horloge la sortie de la bascule recopie la valeur présente sur l'entrée. En réalité les choses sont un peu plus compliquées :

- L'entrée de la bascule doit être stable un certain temps avant l'impulsion d'horloge. Ce temps est appelé temps de *préaffichage* ou setup time en anglais.

- L'entrée de la bascule doit restée stable après l'impulsion. Cette durée correspond au temps de maintien ou hold time en anglais.

- La sortie change avec un certain retard par rapport à l'impulsion d'horloge. Ce retard correspond au *temps de propagation* du signal à travers la bascule.

Ces temps caractéristiques sont valables pour tous les types de bascules synchrones *JK*, *RS*, *T*). Ils sont représentés schématiquement sur la figure 17.

#### Les conséquences.

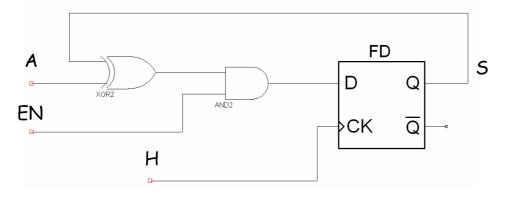

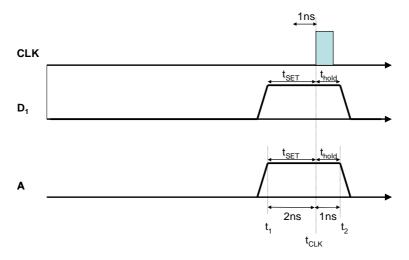

Evidement les contraintes précédentes ne sont pas sans conséquences sur le fonctionnement d'un circuit synchrone. Prenons l'exemple du circuit représenté sur la figure 18.

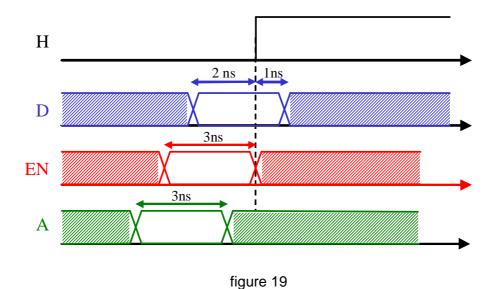

Quelles sont les contraintes sur les variations des entrées A et EN du système pour que les temps de préaffichage et de maintien de la bascule ne soient pas violés? Pour fixer les idées considérons les temps caractéristiques suivants :

- temps de préaffichage (setup time)  $t_{set} = 2 ns$ .

- temps de maintien (hold time)  $t_{hold} = 1 ns$ .

- temps de propagation à travers une porte logique combinatoire  $t_{pc} = 1ns$ .

- temps de propagation à travers la bascule (ou temps de basculement)  $t_{pff} = 1.5 \, ns$ .

La situation est décrite sur le chronogramme de la figure 19. On constate que l'entrée A doit être stable entre 4 ns et 1 ns avant l'impulsion d'horloge.

A titre d'exercice on pourra montrer que si le temps de propagation a travers une porte logique ( $t_{pc}$ ) varie entre 0,4 et 1,5 ns, alors l'entrée A doit être stable entre 5 ns avant et 0,2 ns après l'impulsion d'horloge.

La sortie change 1,5 ns après l'impulsion d'horloge.

figure 18

## 2.5.2. Analyse temporelle d'un circuit.

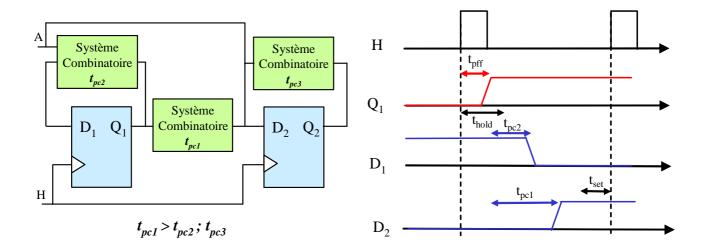

Lors de l'analyse d'un circuit comportant des bascules connectées entre elles par l'intermédiaire de portes combinatoires plusieurs questions se posent. Nous allons les énoncer, et y répondre, en considérant le circuit schématisé sur la figure 20. Sur ce circuit deux bascules D sont reliées entre elles par un bloc combinatoire, la sortie de chacune des bascules également rebouclée sur son entrée.

figure 20

**1.** Les retards introduits par les différents composants entraînent-ils des violations internes du temps de maintien des bascules?

Pour répondre il faut, pour chaque bascule, repérer la boucle la plus courte reliant les entrées et les sorties. Pour chacune des bascule il faut ensuite vérifier que le temps de basculement additionner au temps de propagation à travers les différentes portes logiques est supérieur au temps de maintien de la bascule :

$$t_{pff} + t_{pc2} > t_{hold}$$

$$t_{pff} + t_{pc3} > t_{hold}$$

Si, dans la documentation du circuit, les temps caractéristiques sont donnés sous la forme d'un interval entre une valeur minimum et une valeur maximum, la relation précédente doit bien sûr être vérifiée en utilisant les valeurs minimums des temps caractéristiques (figure 20).

2. Compte tenu du temps de préaffichage des bascules, quelle est la fréquence maximum autorisée pour l'horloge?

On doit s'assurer que les différentes contraintes temporelles sont respectées entre deux impulsions d'horloge. Pour cela on identifie la ou les connexions sortie de bascule – entrée de bascule pour lesquelles les retards accumulés sont maximums. La période minimum de l'horloge est alors, en supposant que  $t_{pc1} > t_{pc2}$  sur la figure 20.

$$T_{\min} = t_{pff} + t_{pc1} + t_{set}$$

Cette fois la condition la plus stricte est obtenue avec les valeurs maximums des temps caractéristiques (figure 20).

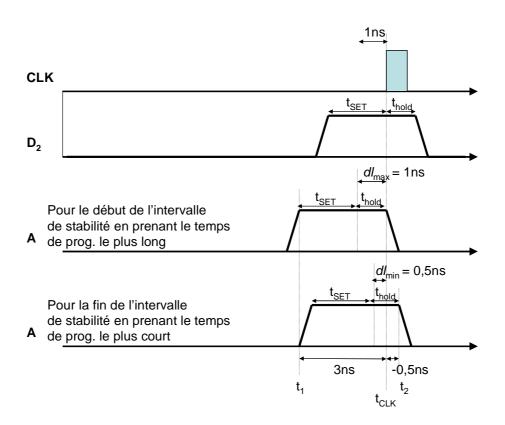

**3.** Durant quelle période (par rapport à l'impulsion d'horloge.) les entrées doivent-elles être stables?

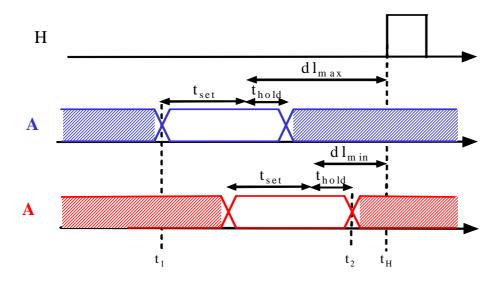

Il faut repérer sur le schéma les valeurs maximum et minimum des retards entre les entrées du circuit et les entrées des bascules, respectivement  $d\ell_{\rm max}$  et  $d\ell_{\rm min}$ . Les deux situations "extrêmes" sont représentées sur le chronogramme de la figure 21. L'entrée A doit être stable entre les instants  $t_1$  et  $t_2$  définis par:

$$t_1 = t_H - (t_{set} + d\ell_{max})$$

$$t_2 = t_H - (d\ell_{\min} - t_{hold})$$

4. A quel moment les sorties sont-elles susceptibles de changer?

Les sorties des bascules commuttent avec le retard  $t_{\it pff}$  par rapport à leurs entrées. A ce retard il faut ajouter les effets des éventuelles portes supplémentaires introduites entre les sorties des bascules et les sorties du circuit.

#### 2.5.3. Exemple du compteur.

On reprend le circuit de la figure 12 et on définit les temps caractéristiques suivants :

- temps de préaffichage (setup time)  $t_{set} = 2ns$ .

- temps de maintien (hold time) t hold = 1ns.

- temps de propagation à travers une porte logique combinatoire  $0.5\,ns < t_{pc} < 1ns$  .

- temps de propagation à travers la bascule  $0,5 ns < t_{pff} < 2 ns$

figure 21

1. Y-a-t-il un risque de violation interne des temps de maintien?

Non pour la bascule 1 :

$$t_{pff,min} + 2xt_{pc,min} = 0,5 ns + 2x0,5 ns > t_{hold} = 1ns$$

Par contre pour la bascule 0 on a :  $t_{pff,min} + t_{pc,min} = 0,5 ns + 0,5 ns = t_{hold} = 1 ns$  ce qui peut poser problème.

2. Quelle est la fréquence maximum autorisée pour l'horloge?

On calcule la période minimum à partir de l'expression :

$$T_{\min} = t_{set} + t_{pff,\max} + 3xt_{pc,\max} = 2ns + 2ns + 3x1ns = 7ns$$

On en déduit la fréquence maximum  $f_{max} = 143 MHz$ .

**3.** A quels moments l'entrée *A* doit-elle être stable?

Sur le schéma on identifie les délais  $d\ell_{\max}=3t_{pc,\max}$  et  $d\ell_{\min}=t_{pc,\min}$ . L'entrée A doit être stable entre  $t_{set}+d\ell_{\max}=2ns+3\times 1ns=5ns$  avant l'impulsion d'horloge et  $d\ell_{\min}+t_{hold}=0$ , 5ns-1ns=-0, 5ns après l'impulsion d'horloge.

**4.** Les sorties du circuit sont directement reliées aux sorties des bascules, elles changent donc entre 0,5 *ns* et 2*ns* après l'impulsion d'horloge.

#### 2.5.4. Remarques.

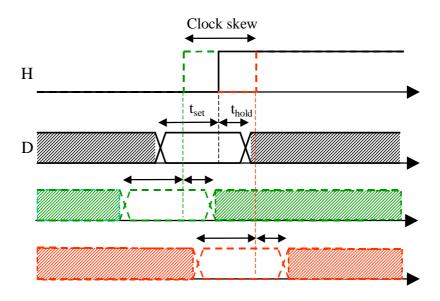

Pour ne pas compliquer les raisonnements précédents, nous avons supposé que les bascules étaient toutes excitées par une horloge parfaitement synchrone. Ceci n'est pas

toujours rigoureusement vrai, les signaux d'horloge. peuvent être légèrement décalés en différents points du circuit. Ce décalage, appelé *clock skew* en anglais, oblige à augmenter les temps de préaffichage et de maintien à prendre en compte lors de l'analyse temporelle d'un circuit (figure 22). Nous verrons dans le chapitre suivant les précautions à prendre pour limiter au maximum cet effet.

figure 22

# 2.6. Exercices corrigés.

Exercice 1 : Analyse d'un système asynchrone classique.

Donner le fonctionnement de la bascule RS (bascule formée de portes NAND) : Schéma, tables de vérité, états stables...

Exercice 2 : Analyse d'un système Asynchrone.

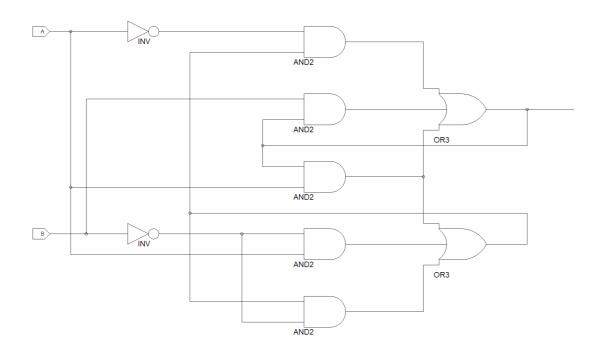

A et B sont des entrées des circuits suivants. Analyser ces deux circuits et interpréter le diagramme des transitions afin de proposer une fonction.

# Exercice 3: Analyse.

**1.** Quelle la différence fondamentale entre le montage suivant et les montages de l'exercice précédent?

**2.** En supposant que ces bascules RS, sensibles aux fronts descendants, ont la table de vérité suivante:

| R                | 0 | 0 | 1              | 1 |

|------------------|---|---|----------------|---|

| S                | 0 | 1 | 1              | 0 |

| Q <sub>n+1</sub> | Х | 1 | Q <sub>n</sub> | 0 |

faire l'étude du circuit en donnant le diagramme de transition. Comment interpréter ce diagramme.

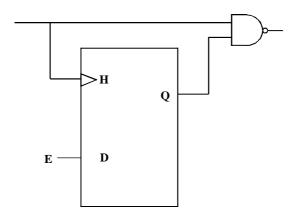

#### Exercice 4 : La bascule D.

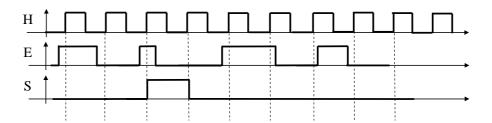

Rappeler la table de vérité de la bascule D. Puis établir le chronogramme du schéma de la figure suivante contenant une bascule D. On suppose que le signal d'horloge envoyé sur l'entrée **H** de la bascule est signal carré.

# Exercice 5 : Analyse d'un système séquentiel.

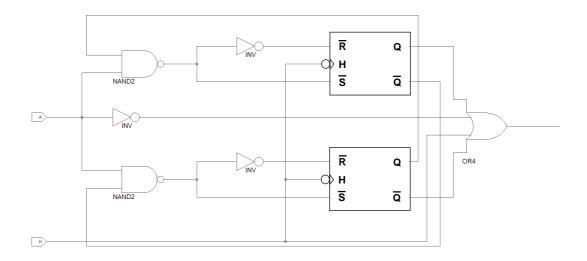

On considère le schéma de la figure 1 réalisé avec des bascules **RS asynchrones à** base de portes NOR.

Figure 1

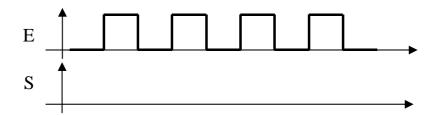

- 1. Analyser le fonctionnement de ce système. On donnera les tables des excitations secondaires et des transitions, et l'on commentera le comportement des bascules 1 et 2 lorsque E = 0 ou E = 1.

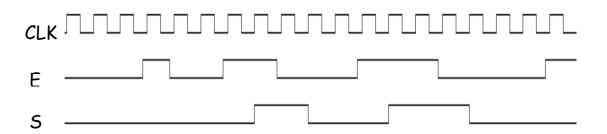

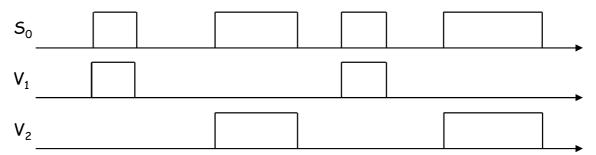

- 2. Compléter le chronogramme suivant.

**3.** Quelle est la fonction réalisée par ce montage? S'agit-il d'un système synchrone ou d'un système asynchrone? justifier clairement votre réponse.

On rappelle que la table des transitions d'une bascule RS à base de portes NOR est :

Exercice 6 : Analyse d'un système.

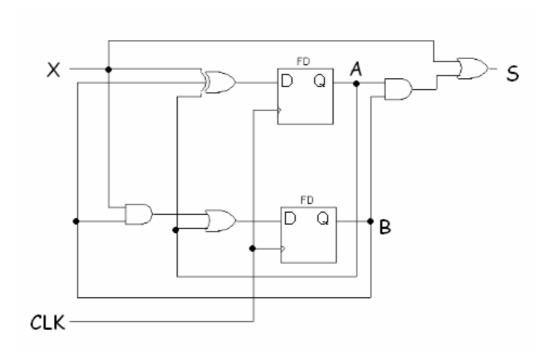

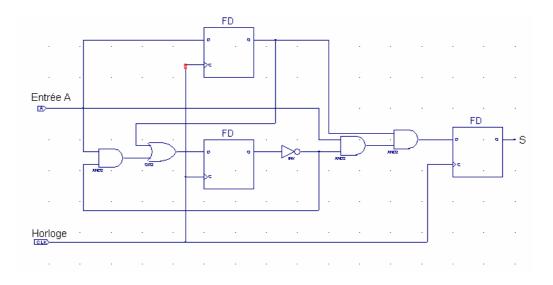

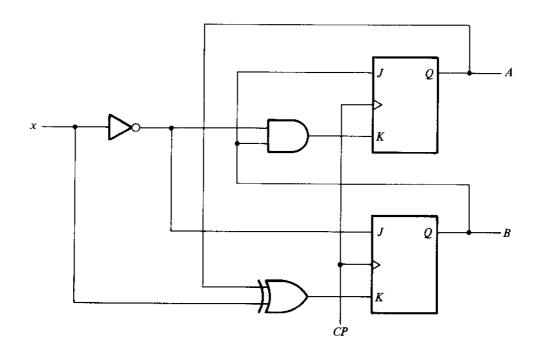

On considère le circuit suivant réalisé avec des bascules D synchrones sensibles à des fronts montants.

- 1. Etablir les équations de commandes des bascules et l'expression de la sortie S.

- **2.** Ecrire la table de transitions reliant les valeurs futures A<sup>+</sup> B<sup>+</sup> en fonction des valeurs présentes A et B. Donner la table de la sortie S

- **3.** Tracer le diagramme d'états.

- **4.** Compléter le chronogramme suivant. On supposera qu'initialement A = B = 0.

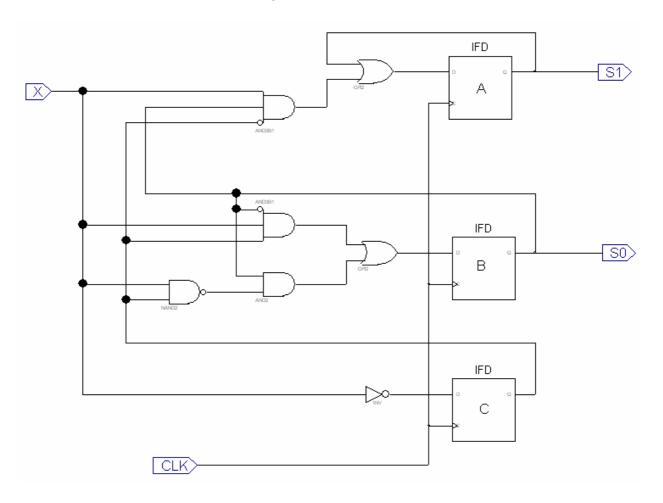

Exercice 7 : Analyse d'un système séquentiel.

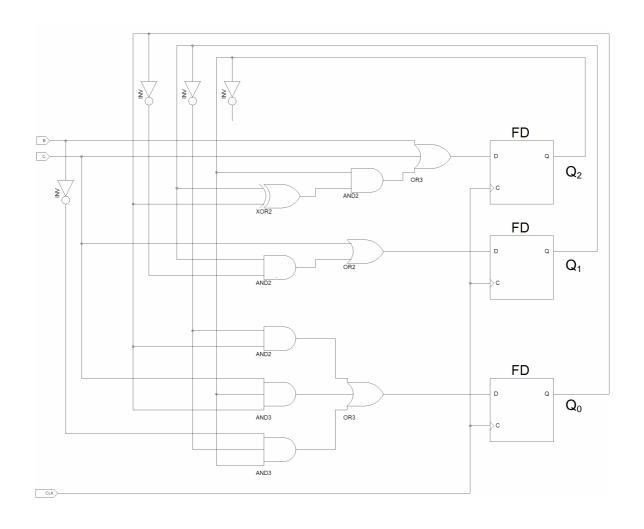

On considère le circuit de la figure suivante réalisé avec des bascules D synchrones sensibles aux fronts montants d'une horloge.

1. Etablir les équations de commandes des entrées D<sub>i</sub> (i = A, B ou C) des bascules.

- **2.** Remplir la table des transitions reliant les valeurs futures Q<sub>i</sub><sup>+</sup> aux valeurs présentes Q<sub>i</sub> et à l'entrée X. Donner la table des sorties.

- 3. Représenter <u>clairement</u> l'évolution du circuit sous la forme d'un diagramme.

- **4.** Compléter le chronogramme suivant. On supposera qu'initialement les sorties des 3 bascules sont au niveau bas.

- **5.** Après que les sorties ont pris la valeurs  $S_1S_0 = 11$ , est-il possible de retrouver une situation ou  $S_1S_0 = 00$  ? Justifier votre réponse.

- **6.** On suppose que les caractéristiques temporelles des différents composants sont les suivantes :

- Le retard  $t_{pc}$  introduit par une porte logique est compris entre 0,5 et 1 ns.

- Le temps de propagation  $t_{pff}$  à travers les bascules est compris entre 1 et 2 ns.

- Les temps de préaffichage et de maintien des bascules sont respectivement  $t_{set} = 2$  ns et  $t_{hold} = 1$  ns

- a. Existe-t-il un risque de violation interne des temps de maintien ?

- b. Quelle est la fréquence maximum de fonctionnement du circuit ?

- c. Pendant quel intervalle de temps l'entrée X doit-elle être constante ?

Exercice 8 : Analyse temporelle d'un montage séquentiel.

- 1. Quels sont les temps caractéristiques utiles à l'étude temporelle (on ne cherche plus à faire l'analyse fonctionnelle) d'un circuit contenant des bascules ? On reprendra les notations du cours :  $t_{set}$ ,  $t_{hold}$ , ...,  $t_{pff}$  (on estime le temps de propagation dans une porte entre 0.25 et 0.5 ns, dans une bascule à 1ns, maintien 1ns et préaffichage 2ns). Donner une brève description de chacune de ces caractéristiques.

- 2. Le circuit présente au moins une rétroaction, quel est la première condition liée au temps de maintien d'une bascule qui doit être satisfaite? On examine ensuite les éventuelles violations qui pourraient se produire entre deux fronts actifs d'horloge. Ces considérations permettront de déterminer la fréquence d'horloge maximum envisageable pour ce montage et ces temps caractéristiques.

- 3. Le dernier point à vérifier est lié à intervalle temporel durant lequel les entrées doivent être stables. Déterminez cet intervalle.

Exercice 1 : Analyse d'un système asynchrone classique.

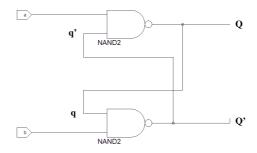

Les circuits des bascules RS (il y a plusieurs versions) sont particulièrement symétriques, on peut donc s'attendre à une fonctionnement symétrique. Le montage d'une bascule RS basée sur l'utilisation de portes NAND :

Ce montage présente deux rebouclages que l'on notera q et q' mais il n'y a aucune horloge ni synchronisation, Nous sommes en présence d'un système séquentiel asynchrone. Vu la relative simplicité du circuit, on pourrait être tenté de réaliser une étude intuitive.

Ici nous réaliserons l'étude exhaustive selon la méthode vue en cours, le lecteur pourra retrouver les résultats par la méthode « économique ».

Les entrées a et b

| а      | 0   | 0   | 1   | 1   |

|--------|-----|-----|-----|-----|

| q q'\b | 0   | 1   | 1   | 0   |

| 0 0    | 1 1 | 1 1 | 1 1 | 1 1 |

| 0 1    | 1 1 | 1 1 | 0 1 | 0 1 |

| 1 1    | 1 1 | 1 0 | 0 0 | 0 1 |

| 1 0    | 1 1 | 1 0 | 1 0 | 1 1 |

QQ'

Dans ce tableau nous calculons l'état futur QQ' pour tous les états initiaux qq' possibles et pour toutes les combinaisons des entrées a et b possibles. Les premières conclusions

concernent la stabilités des états : l'état initial (00) ne sera jamais stable quelque soit la valeur des entrées a et b, en revanche tous les autres états (01), (10) et (11) peuvent être stables.

D'autre part étant donné que notre circuit est asynchrone il faut déterminer la présence d'éventuelles transitions interdites qui correspondent au changement simultané d'au moins deux bits de l'état. Prenons la transition de qq'=11 vers QQ' =00 pour les entrées ab=11. Les deux bits q=1 et q'=1 tombent à zéro, bien sur ils ne tomberont pas exactement au même moment donc en réalité nous auront une transition de 11 vers 10 ou 10 sans pouvoir déterminer l'une ou l'autre. Comme nous pouvons prévoir de manière exacte l'évolution du système il faudra éviter d'utiliser cette transition.

qq'=00 vers QQ' =11 pour les entrées ab=φφ sont aussi des transitions interdites.

L'état (00) n'est pas stable et toutes les transitions partant de cet état sont interdites, il semble préférable, si on peut, d'éviter d'utiliser cet état.

Les cercles représentent les états notés (qq').

Le diagramme des transitions est parfaitement symétrique et on voit qu'il est possible d'avoir un fonctionnement cyclique entre les états (10) et (01) sans utiliser (00). En appliquant b=0, le système décrit la partie gauche avec q=1. En appliquant a=0, le système décrit la partie droite avec q=0. Il faut noter que les sorties sont complémentées. On choisira donc les notations en rapport avec les fonctions des bascules : l'entrées a deviendra Set et b, Reset ; l'état actif est 0 (pour faire un reset on applique 0 à b), on parle alors de bascule  $\overline{R.S.}$ .

| $\overline{S}$ $\overline{R}$ | Sortie Q | fonction            |

|-------------------------------|----------|---------------------|

| 1 1                           | q        | Mémoire ou Interdit |

| 0 1                           | 1        | set                 |

| 1 0                           | 0        | reset               |

| 0 0                           | 1        | RAZ du système      |

Pour résumé, nous avons les fonctions set et reset lorsque les entrées sont complémentées, avec les deux entrées à '1' la dernière valeur est mémorisée et l'état interdit (00) sera à éviter.

Exercice 2 : Analyse d'un système Asynchrone.

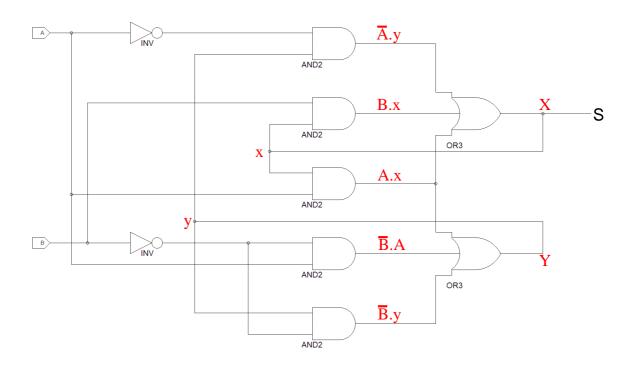

# Premier montage

Nous sommes en présence d'un circuit asynchrone, pas d'horloge ni étage de bascules, par contre nous identifions deux entrées A et B et deux rebouclages ou excitations secondaires X et Y. Nous noterons x et y les variables secondaires. Dans ce genre de montage il est très utile de noter la valeur de sortie de chaque porte. Les excitations secondaires sont :  $X = \overline{A}.y + B.x + A.x$  et  $X = \overline{B}.y + \overline{B}.A + A.x$ .

|      | Α | 0  | 0  | 1  | 1  |

|------|---|----|----|----|----|

| ху \ | В | 0  | 1  | 1  | 0  |

| 0 0  |   | 00 | 00 | 00 | 01 |

| 0 1  |   | 11 | 10 | 00 | 01 |

| 1 1  |   | 11 | 10 | 11 | 11 |

| 1 0  |   | 00 | 10 | 11 | 11 |

Table des excitations secondaires :

| état \ A | 0   | 0   | 1   | 1<br>0 |

|----------|-----|-----|-----|--------|

| present  |     | •   | •   |        |

| 1        | (1) | (1) | (1) | 2      |

| 2        | 3   | х   | 1   | (2)    |

| 3        | (3) | 4   | (3) | (3)    |

| 4        | 1   | (4) | 3   | Х      |

Tables des transitions

**Etats futurs**

Les transitions interdites sont notées « x » afin d'éviter de les inclure dans le diagramme, on note aussi les stabilités des états par des parenthèses. Pour un circuit synchrone, on peut se permettre d'avoir un état non stable (on sait par définition que le système restera une période d'horloge dans cet état non stable). Dans le cas asynchrones, on ne pas prévoir le temps que restera le système dans cet état instable (ce temps est très court et dépend de la propagation et de la commutation des portes). On préfère alors n'avoir que des états stables. Ce qui est le cas ici.

Le diagramme des transitions permet présenter de manière synthétique la valeur des sorties (ici, triviale car S=X) et les transitions, même pour des diagramme avec un faible nombre d'états il est préférable de compter le nombre total de transitions : 16 – 2 transitions interdites = 14. Le système est cyclique et sa fonction repose certainement sur ce cycle, le chronogramme de droite est construit de manière à parcourir le cycle. La séquence

temporelle des entrées A et B nécessaires à cela ainsi que la valeur de la sortie sont facilement interprétables. Un premier bouton poussoir A active la sortie sur son front descendant tandis qu'un second bouton poussoir la désactive.

Remarque: il n'est jamais évident de proposer une fonction pour un circuit à partir de son diagramme d'état. Par contre, on peut conseiller de commencer l'analyser par les caractéristiques suivantes: la stabilité des états et la symétrie du diagramme d'état sont rarement le fruit du hasard et la fonction finale en dépend très certainement. La présence de cycles, de sous-cycles, de cycles imbriqués est capitale. A contrario l'absence de cycle est inquiétante, une machine qui ne marche qu'une fois est a priori mal conçue. Si le résultat de votre analyse amène à un diagramme sans structure ni symétrie évidente, il y a peut-être une erreur.

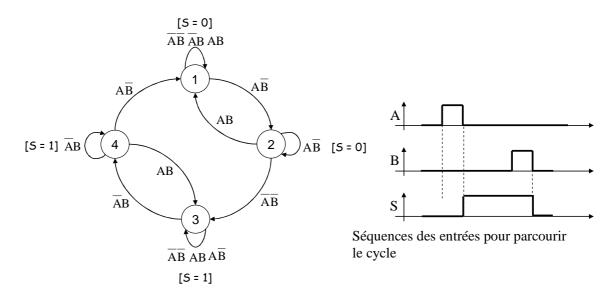

#### Second montage

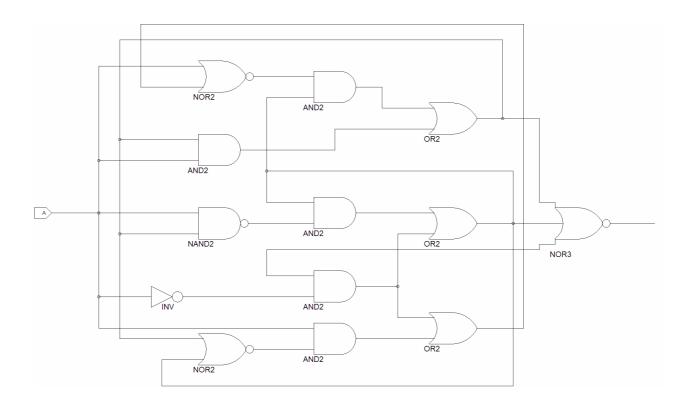

La encore, nous avons 1 entrée et 3 rebouclages notés respectivement X,Y et Z mais aucun bloc séquentiel, le système est donc asynchrone. Les variables secondaires sont

notées respectivement x,y et z. l'étude du schéma donne :

$$X = A.x + \overline{(A+z)}.y$$

$$Y = \overline{A}.z + \overline{A.x}.y$$

et

$$S = \overline{X+Y+Z} = \overline{X} + \overline{Y} + \overline{Z}$$

$$Z = \overline{A}.z + \overline{(x+y)}.A$$

Pour remplir la table des excitations secondaires il est préférable de développer les expressions en mintermes soit

$$X = A.x + \overline{(A+z)}.y = A.x + \overline{A.z}.y$$

$$Y = \overline{A}.z + \overline{A.x}.y = \overline{A}.z + \overline{A}.y + \overline{x}.y$$

$$Z = \overline{A}.z + \overline{(x+y)}.A = \overline{A}.z + \overline{x}.y.A$$

Pour la colonne des excitations secondaires nous avons choisi le code gray, bien sur cela ne change pas le résultat, la lecture sera juste plus ou moins aisée. Par contre étant donné le problème des transitions interdites il vaut prendre un code adjacent. On voit se dessiner une progression d'une ligne à l'autre (une transition état n vers état n+1, pour E=0 et E=1 alternativement).

| A xyz \ | 0     | 1     |

|---------|-------|-------|

| 0 0 0   | (000) | 001   |

| 0 0 1   | 011   | (001) |

| 0 1 1   | (011) | 010   |

| 0 1 0   | 110   | (010) |

| 1 1 0   | (110) | 100   |

| 1 1 1   | 011   | 100   |

| 1 0 1   | 011   | 100   |

| 1 0 0   | 000   | (100) |

Valeurs futures de XYZ

| Eta  |     |     |

|------|-----|-----|

| t \  | 0   | 1   |

| pré  |     |     |

| sent |     |     |

| 1    | (1) | 2   |

| 2    | 3   | (2) |

| 3    | (3) | 4   |

| 4    | 5   | (4) |

| 5    | (5) | 8   |

| 6    | 3   | 8   |

| 7    | 3   | 8   |

| 8    | 0   | (8) |

**ETATS FUTURS**

Remarque : la numérotation des états ne sert qu'à alléger le diagramme et peut-être choisie au hasard.

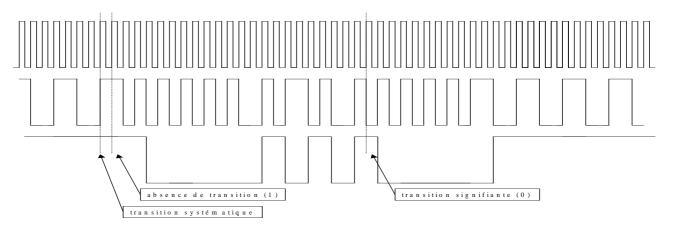

Le diagramme présente clairement une structure cyclique avec un seul état pour lequel la sortie est active. La fonction de ce montage est de reconnaître une séquence temporelle sur l'unique entrée A, la sortie est alors activée jusqu'au prochain front montant sur l'entrée. Cette séquence présentée sur le chronogramme de gauche est composée de 3 créneaux dont les largeurs quelconques. L'alternance (stabilité pour A=x, transition pour A=x) pour l'état n et (stabilité pour A=x, transition pour A=x) pour l'état n+1 est typique des circuits asynchrones.

Remarque: l'analyse montre ici deux états 6 et 7, instables et a priori inaccessibles, ils sont qualifiés d'états parasites. Ils sont présents à chaque fois que le nombre de possibilités de codage des états est supérieur au nombre d'états nécessaire à la fonction. Les trois excitations secondaires permettent 2<sup>3</sup> états possibles alors que seulement 6 états sont nécessaires pour reconnaître la séquence des 3 impulsions sur l'entrée.

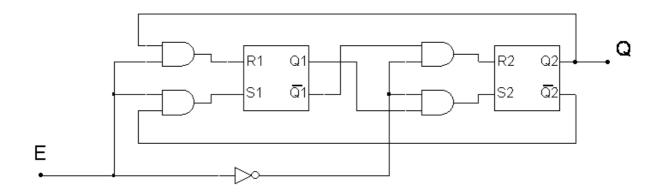

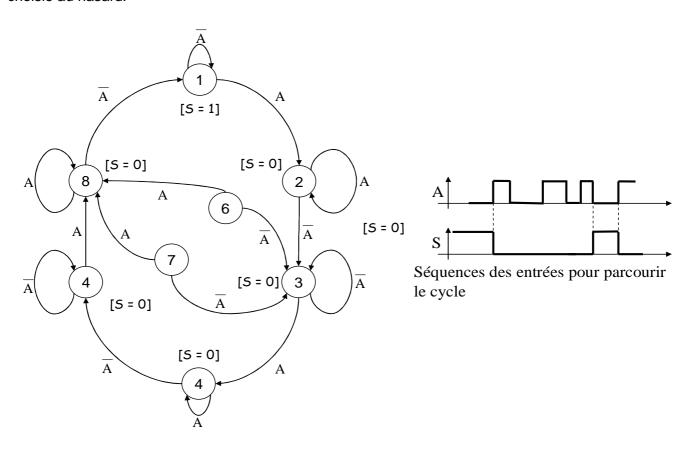

#### Exercice 3: Analyse.

Il faut noter en plus des rebouclages que ce montage présente un bloc synchrone constitué de deux bascules  $\overline{RS}$  synchrones (à la différence de l'exercice 1). Ces bascules ne commutent sous l'effet des entrées  $\overline{R}$  et  $\overline{S}$  (si il y a lieu) que sur un front descendant de l'horloge H. Dans la mesure où la même horloge est appliquée sur les deux bascules, on parle d'un unique bloc synchrone.

Remarque: La méthode d'analyse est la même que pour un circuit asynchrone à ceci près qu'il n'est plus important de se soucier des transitions interdites qui sont donc, à présent, autorisées.

Les entrées  $\overline{RS}$  des bascules sont toujours complémentées pour éviter d'atteindre l'état interdit (on note aussi qu'il n'y aura pas de d'état mémoire seulement des « Set » ou « Reset ») et que les sorties des bascules sont forcement complémentées. Ainsi sur les 4 rebouclages, il ne faut retenir que  $Q_1$  et  $Q_2$  car juste 4 états sont possibles (et non 8, il y a redondance). D'après la table de vérité de la  $\overline{RS}$ ,  $Q_i = R_i$ .

| <b>A</b> q <sub>1</sub> q <sub>2</sub> \ | 0    | 1  |

|------------------------------------------|------|----|

| 0 0                                      | (00) | 01 |

| 0 1                                      | 00   | 11 |

| 1 1                                      | 00   | 10 |

| 1 0                                      | 00   | 00 |

| Excitations secondaires | $Q_1 Q_2$ |

|-------------------------|-----------|

|-------------------------|-----------|

| état A prés ent \ | 0 | 1 | Sortie S |

|-------------------|---|---|----------|

| 1                 | 1 | 2 | 0        |

| 2                 | 1 | 3 | 0        |

| 3                 | 1 | 4 | 0        |

| 4                 | 1 | 1 | 1        |

Etats futurs

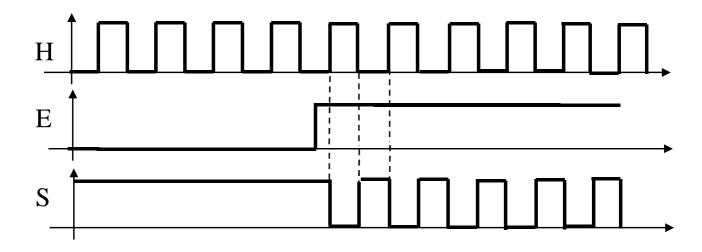

La sortie  $S=Q_1.\overline{A}.H.\overline{Q_2}$  recopie un pulse identique à l'horloge si l'entrée a vaut '0' et si le système se trouve dans l'état 4.

| état <b>A</b><br>présent <b>\</b> | 0                      | 1                                   |

|-----------------------------------|------------------------|-------------------------------------|

| 1                                 | 0                      | 0                                   |

| 2                                 | 0                      | 0                                   |

| 3                                 | 0                      | 0                                   |

| 4                                 | 1                      | 0                                   |

|                                   | $Q_1$ . $\overline{A}$ | $\overline{\Lambda}.\overline{Q_2}$ |

Le chronogramme nous montre bien que la sortie n'est pas synchrone avec l'horloge

mais avec l'entrée, même si le système évolue au rythme de l'horloge la dernière porte logique  $S = Q_1.\overline{A}.H.\overline{Q_2}$  remet en cause cette synchronisation. C'est la distinction entre les structures de Moore (sorties synchrones avec l'horloge) et de Mealy (sorties synchrones avec l'une des entrées).

#### Exercice 4: La bascule D.

La bascule D recopie la valeur de son entrée D manière à chaque front actif de l'horloge. Comme dans l'énoncé rien n'est précisé à cet égard, nous supposerons, comme c'est majoritairement le cas que le front montant est actif.

Cet exercice est assez piégeur puisque pour ce type de montage relativement simple, nous avons tendance à se demander si il est possible de faire l'économie d'une analyse fonctionnelle exhaustive en perdant de vue la structure du circuit. Alors que la seule première question pertinente à se poser est la présence ou non de rebouclage. Il n'y en a pas le système n'étant donc pas séquentiel, la valeur des sorties de dépendent pas de la valeur précédente. L'étude est donc triviale.

Au front montant suivant la transition de E, Q passe à 1 et la sortie devient alors le complément de l'horloge.

#### Exercice 5 : Analyse d'un système séquentiel.

1. Les variables secondaires, facilement identifiables sur le schéma, sont  $q_1$  et  $q_2$ . Les entrées de chacune des bascules s'écrivent alors :

$$R_1 = E \bullet q_2, \quad S_1 = E \bullet \overline{q_2}, \quad R_2 = \overline{E} \bullet \overline{q_1}, \quad S_2 = \overline{E} \bullet q_1$$

Ainsi pour E=0 la bascule 1 est en position mémoire ( $R_1=S_1=0$ ) et la bascule 2 recopie les sorties de la bascule 1 ( $R_2=\overline{q_1}, S_2=q_1$ ). A l'inverse lorsque E=1 c'est la bascule 2 qui est en position mémoire ( $R_2=S_2=0$ ). Ce type de structure, appelée maître-esclave, est à la base des bascules synchrones.

A partir de la table des excitations secondaires d'une bascule RS a base de NOR rappelée dans l'énoncé, on obtient la table des excitations secondaires du système étudié.

| <b>q</b> <sub>1</sub> <b>q</b> <sub>2</sub> | E = 0 | E = 1 |

|---------------------------------------------|-------|-------|

| 0 0                                         | 0 0   | 1 0   |

| 0 1                                         | 0 0   | 0 1   |

| 1 1                                         | 1 1   | 0 1   |

| 1 0                                         | 1 1   | 1 0   |

$Q_1, Q_2$

La table des transitions s'obtient alors facilement :

$0 \ 0 \rightarrow \text{ état } 1$

$0 1 \rightarrow \text{ \'etat } 2$

1 1  $\rightarrow$  état 3

$1 0 \rightarrow \text{ \'etat } 4$

| présent | E = 0 | E = 1 |

|---------|-------|-------|

| 1       | 1     | 4     |

| 2       | 1     | 2     |

| 3       | 3     | 2     |

| 4       | 3     | 4     |

États futurs

Puisque le système est à priori asynchrone, nous avons indiqué les états stables en gras. La sortie S est donnée par  $S=Q_2$  et le diagramme des transitions est alors :

2. On obtient le chronogramme suivant :

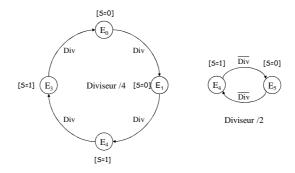

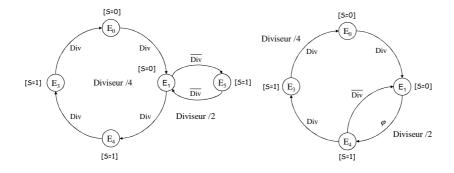

3. C'est un diviseur de fréquence par 2, actif sur le front descendant de l'entrée E. Il s'agit d'un système synchrone puisque les changements d'état se produisent au moment où l'entrée E reçoit une impulsion.

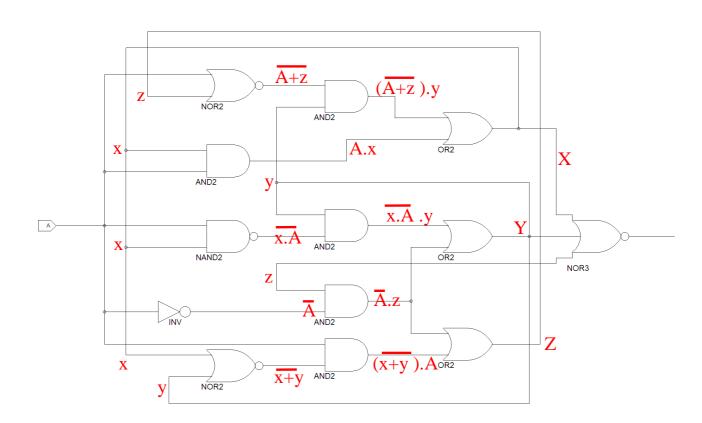

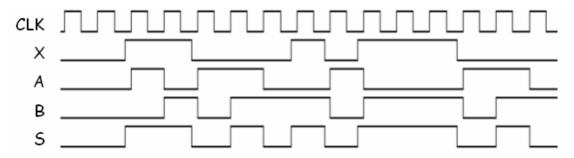

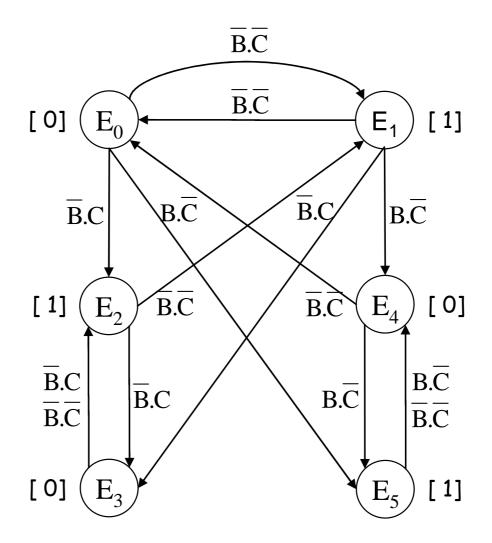

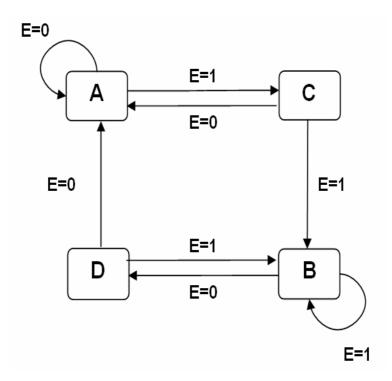

Exercice 6 : Analyse d'un système.

- 1. On établi directement : D<sub>A</sub> = X ⊕ A ⊕ B, D<sub>B</sub> = X B + A et S = X + A B A la différence du montage de l'exercice 1 la sortie S dépend directement de l'entrée X. La sortie change donc simultanément avec l'entrée X et non plus lorsque le système change d'état. Ce type de système est appelé une machine de Mealy.

- 2. Pour une bascule D la valeur future de la sortie est la valeur présente sur l'entrée. On obtient ainsi :

| A B | X = 0                         | X= 1 |  |

|-----|-------------------------------|------|--|

| 0 0 | 0 0                           | 1 0  |  |

| 0 1 | 1 0                           | 0 1  |  |

| 1 1 | 0 1                           | 1 1  |  |

| 1 0 | 1 1                           | 0 1  |  |

|     | A <sup>+</sup> B <sup>+</sup> |      |  |

| X = 0 | X = 1 |  |

|-------|-------|--|

| 0     | 0     |  |

| 0     | 1     |  |

| 1     | 1     |  |

| 0     | 1     |  |

| S     |       |  |

3. En établissant le diagramme d'états il faut bien faire apparaître que la sortie S ne dépend plus uniquement de l'état du système mais aussi de l'entrée X. Pour un même état on peut avoir deux valeurs différentes de la sortie. Par exemple, lorsque le système est dans l'état AB = 01 la sortie vaut 1 si X = 1 et 0 si X = 0. En adoptant la numérotation suivante pour les 4 états :

| 0 0 → 0 | 1 0 → 2 |

|---------|---------|

| 0 1 → 1 | 1 1 → 3 |

On obtient le diagramme d'états.

Depuis l'état 2 (A B = 1 0) la sortie Y = X + A • B vaut 0 ou 1 selon la valeur de X et évolue en même temps que l'entrée. Par contre l'évolution vers l'état futur (ici 1 ou 3) ne se fait que au moment des impulsions d'horloge.

# 4. On obtient alors le chronogramme:

Encore une fois les variations de la sortie peuvent être simultanées avec les variations de l'entrée et non pas uniquement avec celles de l'horloge.

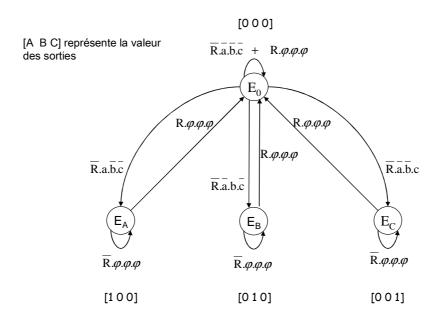

# Exercice 7 : Analyse d'un montage séquentiel.

1. les équations des commandes des bascules s'expriment en fonction des excitations secondaires :

$$\begin{split} D_{A} &= Q_{A} + Q_{B}.\overline{Q_{C}}.X \\ D_{B} &= Q_{B}.\overline{Q_{C}.X} + \overline{Q_{B}}.Q_{C}.X \\ D_{C} &= \overline{X} \end{split} \qquad \text{et} \qquad \begin{aligned} S_{1} &= Q_{A} \\ S_{0} &= Q_{B} \end{aligned}$$

2. le tableau des excitations secondaires :

| Q <sub>A</sub> Q <sub>B</sub> Q <sub>C</sub> | X = 1 | X = 0 |

|----------------------------------------------|-------|-------|

| 0 0 0                                        | 000   | 0 0 1 |

| 0 0 1                                        | 010   | 0 0 1 |

| 0 1 0                                        | 110   | 011   |

| 0 1 1                                        | 000   | 011   |

| 1 0 0                                        | 100   | 101   |

| 1 0 1                                        | 110   | 101   |

| 1 1 0                                        | 110   | 111   |

| 1 1 1                                        | 100   | 111   |

| S <sub>1</sub> | S <sub>0</sub> |

|----------------|----------------|

| 0              | 0              |

| 0              | 0              |

| 0              | 1              |

| 0              | 1              |

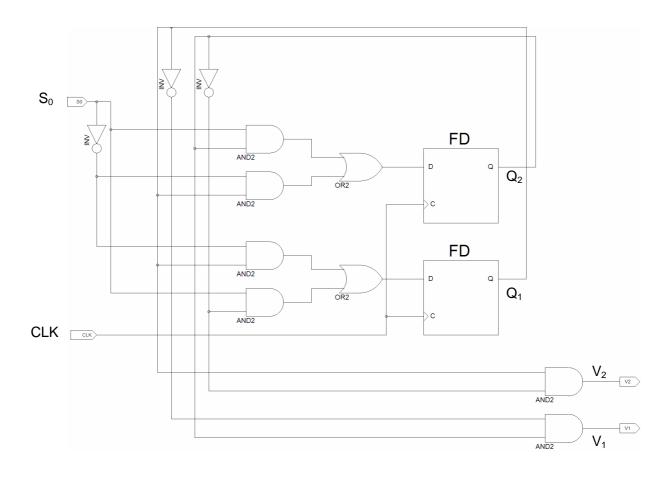

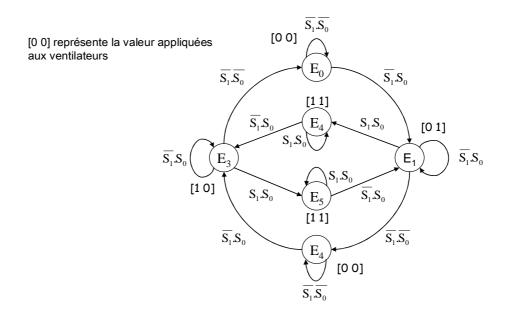

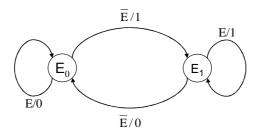

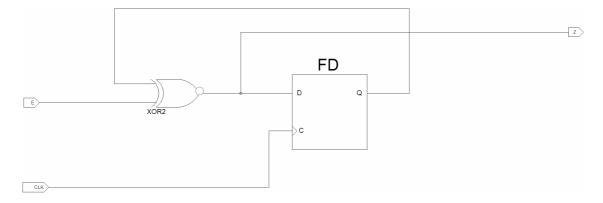

| 1              | 0              |